# 3N190/3N191

Over 30 Years of Quality Through Innovation

**Dual P-Channel Enhancement Mode MOSFET**

# LOW TOTAL HARMONIC DISTORTION (THD) AND VOLTAGE NOISE MOSFET

| FEATURES                                         |                          |  |  |  |  |

|--------------------------------------------------|--------------------------|--|--|--|--|

| DIRECT REPLACEMENT FOR INTERSIL 3N190 & 3N191    |                          |  |  |  |  |

| LOW GATE LEAKAGE CURRENT                         | l <sub>GSS</sub> ≤ ±10pA |  |  |  |  |

| LOW TRANSFER CAPACITANCE                         | C <sub>rss</sub> ≤ 1.0pF |  |  |  |  |

| ABSOLUTE MAXIMUM RATINGS <sup>1</sup>            |                          |  |  |  |  |

| @ 25 °C (unless otherwise stated)                |                          |  |  |  |  |

| Maximum Temperatures                             |                          |  |  |  |  |

| Storage Temperature                              | -65 to +150 °C           |  |  |  |  |

| Operating Junction Temperature                   | -55 to +135 °C           |  |  |  |  |

| Maximum Power Dissipation @ TA=25 <sup>o</sup> C |                          |  |  |  |  |

| Continuous Power Dissipation One Side            | 300mW                    |  |  |  |  |

| Continuous Power Dissipation Both Sides          | 525mW                    |  |  |  |  |

| Maximum Current                                  |                          |  |  |  |  |

| Drain to Source <sup>2</sup>                     | 30mA                     |  |  |  |  |

| Maximum Voltages                                 |                          |  |  |  |  |

| Drain to Gate <sup>2</sup>                       | 40V                      |  |  |  |  |

| Drain to Source <sup>2</sup>                     | 40V                      |  |  |  |  |

| Gate to Gate                                     | ±60V                     |  |  |  |  |

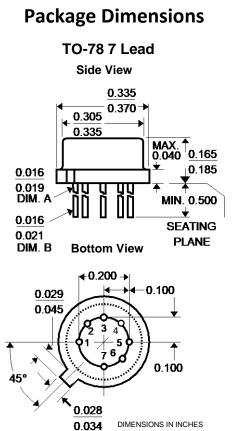

Package Photo TO-78 7L

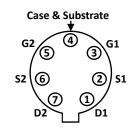

Pin Configuration TO-78 7L

Side View

**Top View**

## Features

- Very High Input Impedance

- High Gate Breakdown

- Low Capacitance

- High Switching Frequency

### Benefits

- Minimal Response Time.

- Generates less heat loss compared to BJT at high currents.

- Great at amplifying analog signals.

Reduces design complexity in

- medium and low power applications.Ideal Choice for high-side switches.

- Simplified gate driving technique reduces overall cost.

## Applications

- Switching Applications

- Amplifying Circuits

- Chopper Circuits

- High-Frequency Amplifier

- Voltage Regulator Circuits

- Inverter

- DC Brushless Motor Drives

- DC Relay

- Digital Circuits

## Description

The 3N190/3N191 Series is a Dual, P-Channel, Enhancement Mode MOSFET. The MOSFET is a voltage controlled solid state device. The simplicity of the design is advantageous for nonisolated POL(Point of Load) power supplies and low-voltage drives applications, where space is limited. The simplified gate driving technique is often a beneficial characteristic for designers because it reduces overall cost. The 3N190/3N191 Series has a very high switching frequency so that they are used in highspeed load switching, given their minimal response time. The 3N190/3N191 can be used for digital control of higher current and higher voltage loads than the ratings that a microcontroller can withstand. They are great at amplifying analog signals, especially in audio applications. They have multiple functions in different types of applications and can also be used as a chopper or regulator. The 3N190 and 3N191 are the same products as a second source for Intersil products.

# **Dual P-Channel Enhancement Mode MOSFET**

| SYMBOL                              | CHARACTERISTIC                                                                 | MIN  | TYP | MAX | UNITS | CONDITIONS                                                                 |

|-------------------------------------|--------------------------------------------------------------------------------|------|-----|-----|-------|----------------------------------------------------------------------------|

| $g_{\rm fs1}/g_{\rm fs2}$           | Forward Transconductance Ratio                                                 | 0.85 | -   | 1.0 | -     | $V_{DS} = -15V, I_D = -500\mu A, f = 1kHz$                                 |

| V <sub>GS1-2</sub>                  | Gate to Source Threshold Voltage<br>Differential                               | -    | -   | 100 | mV    | V <sub>DS</sub> = -15V, I <sub>D</sub> = -500µA                            |

| ΔV <sub>GS1-2</sub><br>ΔT           | Gate to Source Threshold Voltage<br>Differential with Temperature <sup>4</sup> | -    | 50  | -   | µV/°C | $V_{DS} = -15V, I_D = -500\mu A$<br>$T_S = -55 \text{ to } +25 \text{ °C}$ |

| $\frac{\Delta V_{GS1-2}}{\Delta T}$ | Gate to Source Threshold Voltage<br>Differential with Temperature <sup>4</sup> | -    | 50  | -   |       | $V_{DS} = -15V$ , $I_D = -500\mu A$<br>$T_S = +25$ to +125 °C              |

#### MATCHING CHARACTERISTICS @ 25 °C (unless otherwise stated)

#### ELECTRICAL CHARACTERISTICS @ 25 °C

| SYMBOL                        | CHARACTERISTIC                        | MIN  | TYP | MAX   | UNITS | CONDITIONS                                                     |                                  |

|-------------------------------|---------------------------------------|------|-----|-------|-------|----------------------------------------------------------------|----------------------------------|

| BV <sub>DSS</sub>             | Drain to Source Breakdown Voltage     | -40  | -   | -     | V     | I <sub>D</sub> = -10µA                                         |                                  |

| BV <sub>SDS</sub>             | Source to Drain Breakdown Voltage     | -40  | -   | -     |       |                                                                | $I_S = -10\mu A$ , $V_{BD} = 0V$ |

| Vgs                           | Gate to Source Voltage                | -3.0 | -   | -6.5  |       | V <sub>DS</sub> = -15V, I <sub>D</sub> = -500µA                |                                  |

| V <sub>GS(th)</sub>           | Gate to Source Threshold Voltage      | -2.0 | -   | -5.0  |       | $V_{DS} = V_{GS}, I_D = -10 \mu A$                             |                                  |

| - 00(11)                      |                                       | -2.0 | -   | -5.0  |       | V <sub>DS</sub> = -15V, I <sub>D</sub> = -500µA                |                                  |

| Igssr                         | Reverse Gate Leakage Current          | -    | -   | 10    |       | $V_{GS} = 40V$                                                 |                                  |

| I <sub>GSSF</sub>             | Forward Gate Leakage Current          | -    | -   | -10   | pА    | $V_{GS} = -40V$                                                |                                  |

| IDSS                          | Drain Leakage Current "Off"           | -    | -   | -200  |       | V <sub>DS</sub> = -15V                                         |                                  |

| Isds                          | Source to Drain Leakage Current "Off" | -    | -   | -400  |       | $V_{SD} = -15V, V_{DB} = 0V$                                   |                                  |

| I <sub>D(on)</sub>            | Drain Current <sup>2</sup>            | -5.0 | -   | -30.0 | mA    | $V_{DS} = -15V, V_{GS} = -10V$                                 |                                  |

| I <sub>G1G2</sub>             | Gate to Gate Isolation Current        | -    | -   | ±1.0  | μA    | $V_{G1G2} = \pm 80V, I_D = I_S = 0 = mA$                       |                                  |

| <b>g</b> fs                   | Forward Transconductance <sup>4</sup> | 1500 | -   | 4000  | μS    | V <sub>DS</sub> = -15V, I <sub>D</sub> = -5mA, <i>f</i> = 1kHz |                                  |

| gos                           | Output Admittance                     | -    | -   | 300   |       |                                                                |                                  |

| rds(on)                       | Drain to Source "On" Resistance       | -    | -   | 300   | Ω     | $V_{DS} = -20V, I_{D} = -100 \mu A$                            |                                  |

| Crss <sup>3</sup>             | Reverse Transfer Capacitance          | -    | -   | 1.0   |       |                                                                |                                  |

| Ciss <sup>3</sup>             | Input Capacitance Output Shorted      | -    | -   | 4.5   | pF    | $V_{DS} = -15V, I_D = -5mA, f = 1MHz$                          |                                  |

| C <sub>oss</sub> <sup>3</sup> | Output Capacitance Input Shorted      | -    | -   | 3.0   |       |                                                                |                                  |

#### **3N190/191 P-CHANNEL ENHANCEMENT MODE MOSFET** TO-78 7L Substrate (Case) Pin-4 Biasing Recommendation

In order to improve the overall product performance, we strongly recommend Substrate (Case) pin to be connected to highest VCC potential at Pin-4 with an optional  $10K\Omega$  resistor. This ensures strong reverse biasing of junction isolation diode and resulting improvement in Total Harmonic Distortion (THD) and Voltage Noise (Vn) performances. This applied voltage must be maximum 38V which is 2.0V less than device BVDSS breakdown voltage of 40V-max.

#### SWITCHING CHARACTERISTICS

| SYMBOL                          | CHARACTERISTIC     | MIN | TYP | MAX | UNITS | CONDITIONS                             |

|---------------------------------|--------------------|-----|-----|-----|-------|----------------------------------------|

| t <sub>d(on)</sub> <sup>3</sup> | Turn On Delay Time | -   | -   | 15  |       | $V_{DD} = -15V, I_{D(on)} = -5mA,$     |

| tr <sup>3</sup>                 | Turn On Rise Time  | -   | -   | 30  | ns    | $R_{G} = R_{L} = 1.4 k\Omega$          |

| toff <sup>3</sup>               | Turn Off Time      | -   | -   | 50  |       | $M_{\rm G} = M_{\rm L} = 1.4M_{\rm M}$ |

# 3N190/3N191

## **Dual P-Channel Enhancement Mode MOSFET**

### Notes

- 1. Absolute maximum ratings are limiting values above which serviceability may be impaired.

- 2. Per Transistor.

- 3. For design reference only. Not 100% tested.

- 4. Measured at end points,  $T_A$  and  $T_B$ .

5. All characteristics MIN/TYP/MAX numbers are absolute values. Negative values indicate electrical polarity only.

Information furnished by Linear Integrated Systems is believed to be accurate and reliable. However, no responsibility is assumed for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Linear Integrated Systems.

# **Ordering Information**

Standard Part Call-Out

3N190 TO-78 7L RoHS

3N191 TO-78 7L RoHS

Custom Part Call-Out (Custom Parts Include SEL + 4 Digit Numeric Code)

3N190 TO-78 7L RoHS SELXXXX

3N191 TO-78 7L RoHS SELXXXX