# INEAR SYSTEMS

Linear Systems

**Quality Through Innovation Since 1987**

# **Table of Contents:**

| Testimonials                                                 | 4        |

|--------------------------------------------------------------|----------|

| Introduction                                                 |          |

| Ordering Information and Sampling Policy                     | 5        |

| Quality and Reliability                                      | 6        |

| Discrete Component Product Line Begins                       | 7        |

| N-Channel Dual JFETs                                         |          |

| LSK389 Series (Ultra Low Noise )                             | 8-15     |

| LSK489 Series (Low Noise, Input Capacitance and Distortion ) | 16-22    |

| LS840 Series (Low Noise )                                    | 23-24    |

| LS844 Series (Low Noise )                                    | 25-32    |

| LS5911 Series (High Frequency )                              | 33-35    |

| SST/U440 Series (High Frequency )                            | 36-37    |

| LS830 Series (Low Leakage and High Impedance)                | 38-39    |

| 2N/LS5905 Series (Low Leakage and High Impedance)            | 40-41    |

| SST/U421 Series (Low Leakage and High Impedance)             |          |

| SST/U401 Series (General Purpose)                            |          |

| 2N/LS3954 Series (General Purpose)                           | 46-47    |

| LSK589 (General Purpose)                                     |          |

| N-Channel Single JFETs                                       |          |

| LSK170 Series (Ultra Low Noise )                             | 50-56    |

| LSK189 (Ultra Low Noise )                                    |          |

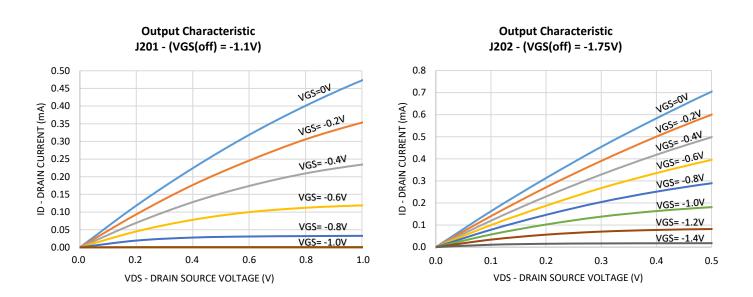

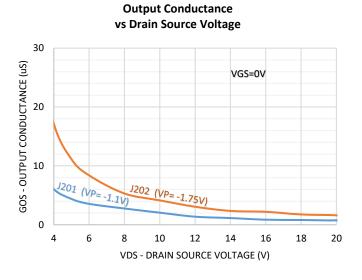

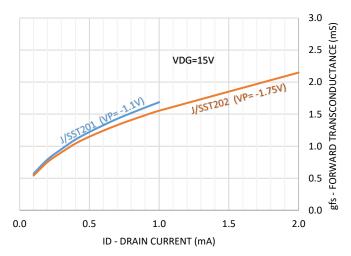

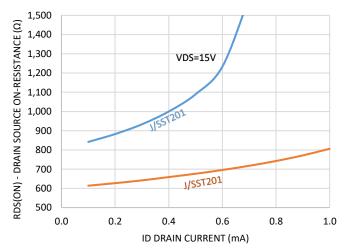

| J/SST201 Series (Low Noise)                                  |          |

| LS846 (Low Noise)                                            |          |

| LSK170X (Low Noise, High IDSS)                               |          |

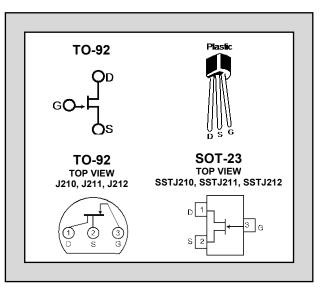

| <u>2N/PN/SST4416 Series</u> (High Frequency)                 |          |

| J/SST210 Series (High Frequency)                             |          |

| J/SST/U308 Series (High Frequency )                          |          |

| LS/PF/SST5301 (Low Leakage and High Impedance)               |          |

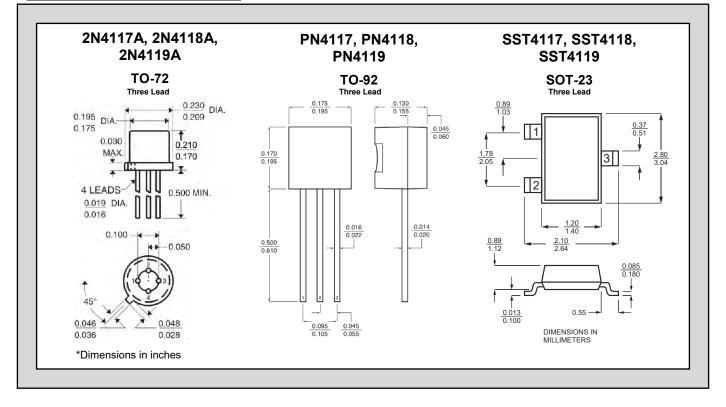

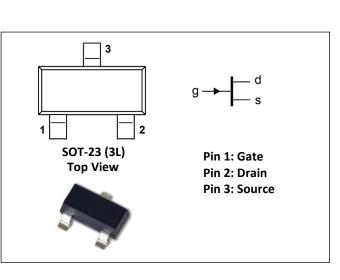

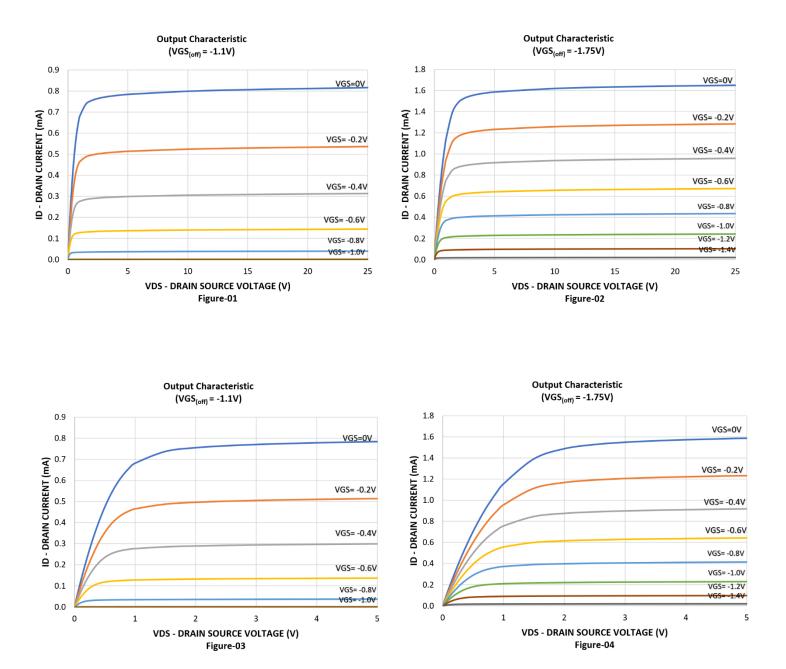

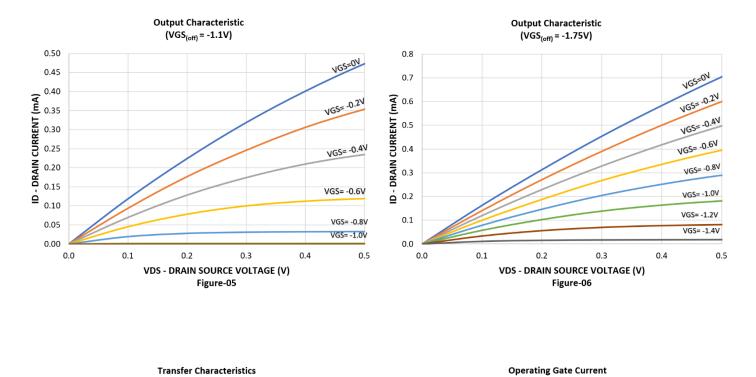

| <u>2N/PN/SST4117 Series</u> (Low Leakage and High Impedance) |          |

| <u>LSBF510</u> (High Gain)                                   |          |

| <u>LS190</u> (General Purpose)                               |          |

| N-Channel Single JFET Switches                               | 05 00    |

| <u>2N/PN/SST4391 Series</u> (General Purpose)                | 87-89    |

| 4391DFN Series (General Purpose DFN Package)                 |          |

| J/SST111 Series (General Purpose)                            |          |

| P-Channel Single JFET Switches                               | 55 5 1   |

| 2N5018 (General Purpose)                                     | 95-96    |

| 2N5114 Series (General Purpose)                              |          |

| J/SST174 Series (General Purpose)                            |          |

| Low Leakage Single Diodes                                    | 55 100   |

| <u>J/SST/PAD Series</u> (Pico Ampere)                        | 101-102  |

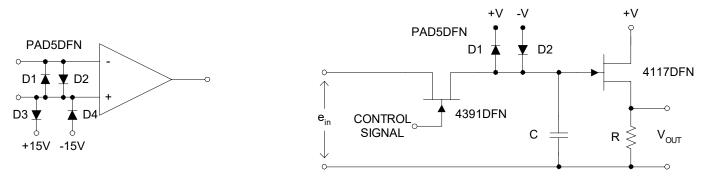

| PAD Series DFN Package (Pico Ampere DFN Package)             |          |

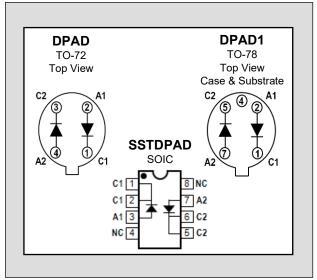

| Low Leakage Dual Diodes                                      | 100 10 1 |

| DPAD/ SSTDPAD Series (Pico Ampere)                           | 105-106  |

| <u>ID100 Series</u> (Pico Ampere)                            |          |

| <u>N-Channel Lateral Single DMOS FET Switches</u>            | 107 100  |

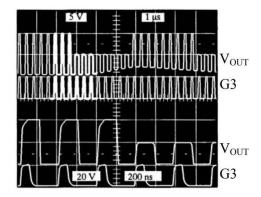

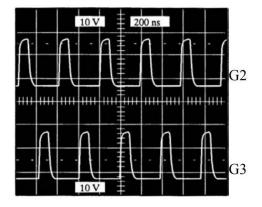

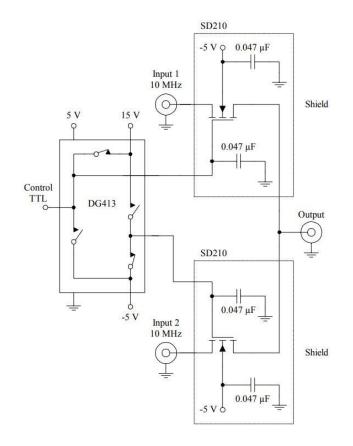

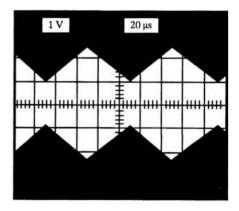

| <u>SD/SST210 Series</u> (High Speed)                         | 109-111  |

| <u>SD/SST210 Series</u> (High Speed Zener Protected)         |          |

| N-Channel Lateral Quad DMOS FET Switches                     | ±±£ ±±Ŧ  |

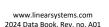

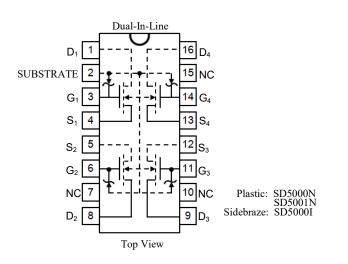

| <u>SD5000 Series</u> (High Speed Zener Protected)            | 115-117  |

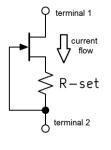

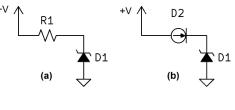

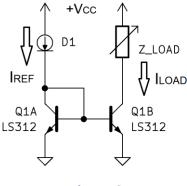

| Current Regulating Diodes                                    |          |

| <u>SST500 Series</u> (Low Impedance)                         | 118-119  |

| Bipolar Dual NPN Transistors                                 |          |

| <u>IT120 Series</u> (General Purpose)                        | 120-121  |

|                                                              |          |

# **Table of Contents Continued:**

| LS3250 Series (Low Noise)                                                                            | 122-126 |

|------------------------------------------------------------------------------------------------------|---------|

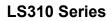

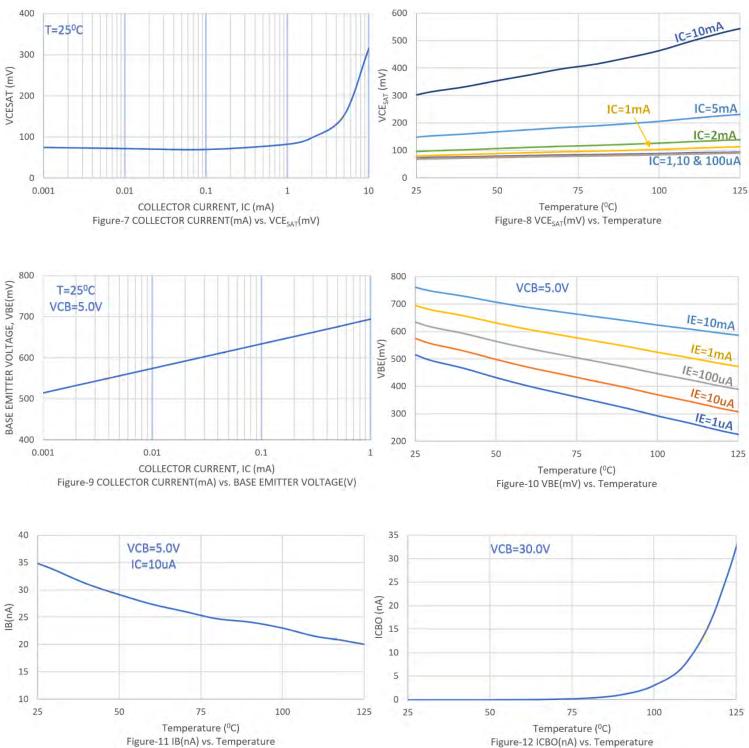

| LS310 Series (General Purpose)                                                                       | 127-132 |

| Bipolar Dual Super Beta NPN Transistors                                                              |         |

| LS301 Series (General Purpose)                                                                       | 133-134 |

| Bipolar Log Conformance Dual NPN Transistor                                                          |         |

| LS318 (General Purpose)                                                                              | 135-136 |

| Bipolar Dual PNP Transistors                                                                         |         |

| IT130 Series (General Purpose)                                                                       | 137-138 |

| LS350 Series (General Purpose)                                                                       | 139-140 |

| LS3550 Series (Low Noise)                                                                            | 141-142 |

| Bipolar Single PNP Transistors                                                                       |         |

| LS3550 Single Series (General Purpose)                                                               | 141-142 |

| Bipolar Log Conformance Dual PNP Transistor                                                          |         |

| LS358 (General Purpose)                                                                              | 143-144 |

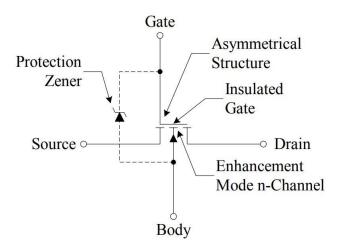

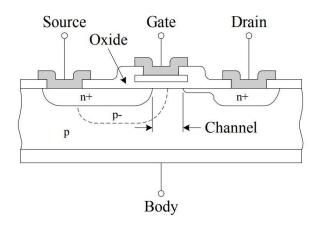

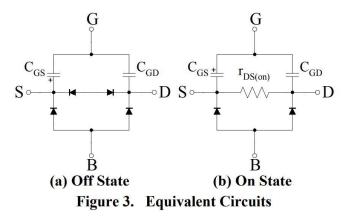

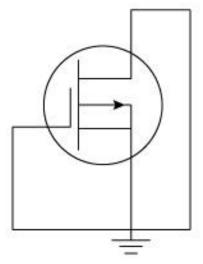

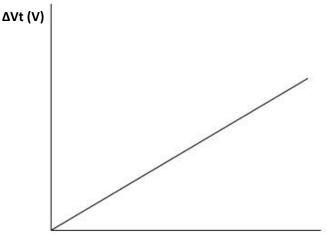

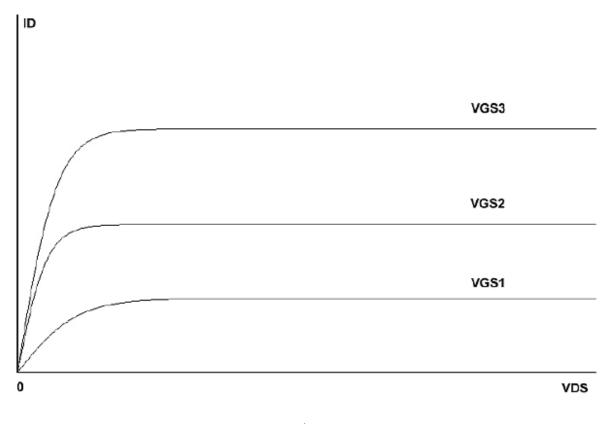

| N-Channel Enhancement Mode Single MOSFETs                                                            |         |

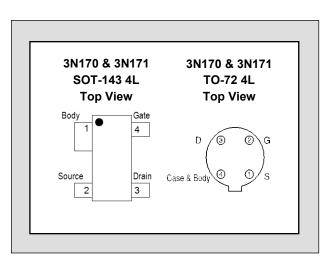

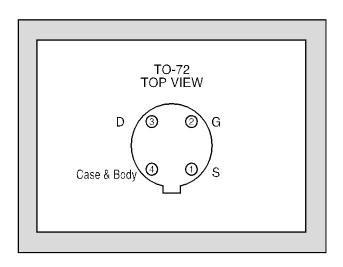

| <u>3N170 Series</u> (General Purpose )                                                               | 145-146 |

| 2N4351 Series (General Purpose )                                                                     | 147-148 |

| P-Channel Enhancement Mode Single MOSFETs                                                            |         |

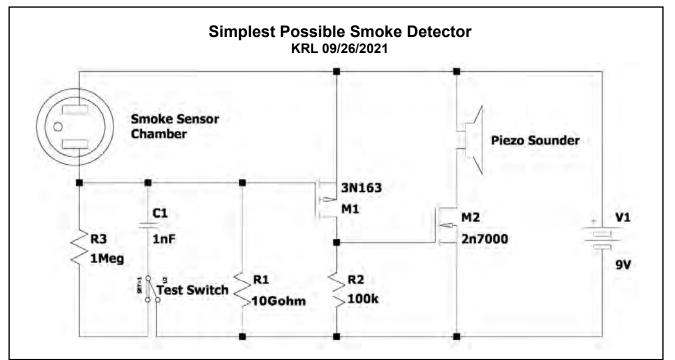

| 3N163 Series (General Purpose)                                                                       | 149-151 |

| P-Channel Enhancement Mode Dual MOSFETs                                                              |         |

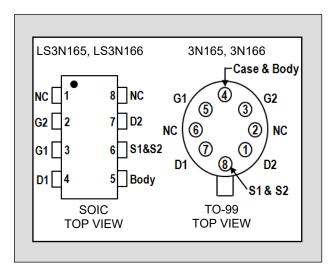

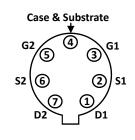

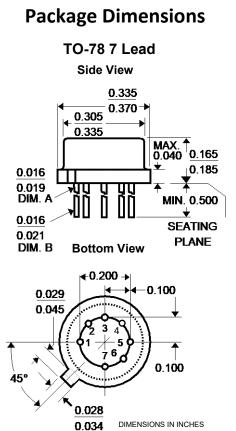

| <u>3N165 Series</u> (General Purpose)                                                                | 152-153 |

| 3N190 Series (General Purpose)                                                                       | 154-156 |

| Single BIFET Amplifier                                                                               |         |

| LS320 (High Input Impedance)                                                                         | 157-158 |

| N-Channel JFET VCR (Voltage Controlled Resistor)                                                     |         |

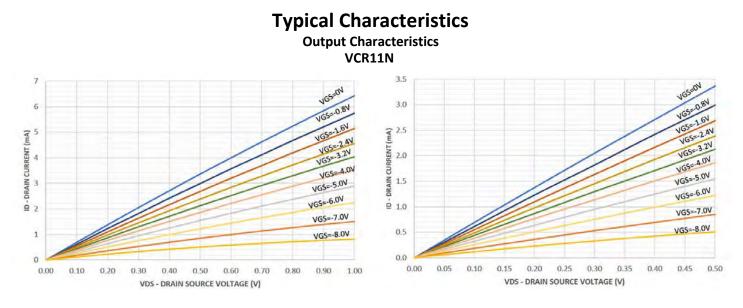

| <u>VCR11N</u> (Rds(on)=100 to 200Ω and Rds(on)=14 to 38Ω)                                            | 159-160 |

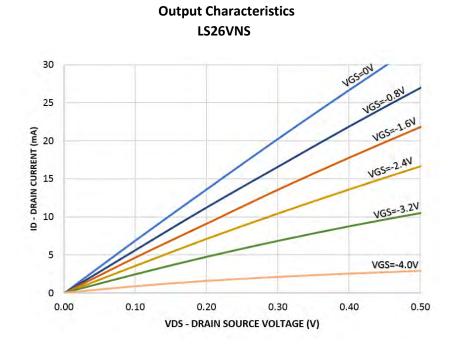

| LS26VNS (Rds(on)=100 to 200Ω and Rds(on)=14 to 38Ω)                                                  |         |

| P-Channel JFET VCR (Voltage Controlled Resistor)                                                     |         |

|                                                                                                      | 164-166 |

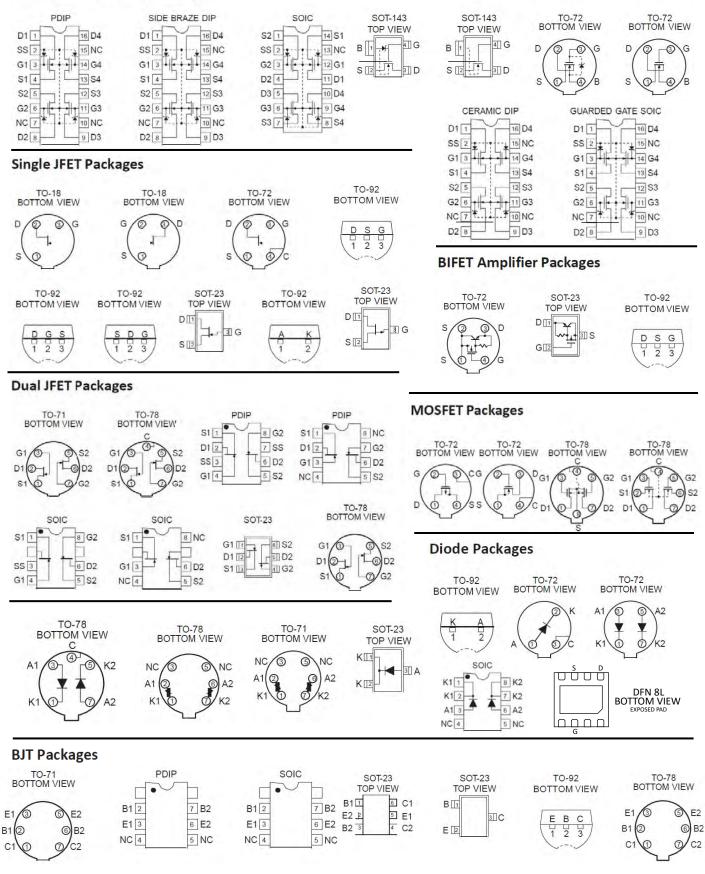

| Package Options                                                                                      |         |

| Application Notes                                                                                    |         |

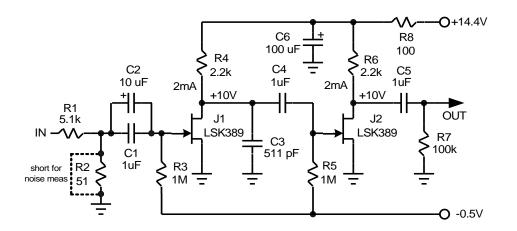

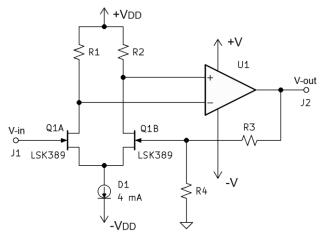

| LSK389 Application Note                                                                              |         |

| Common Mode Rejection Ratio in Dual JFETs                                                            |         |

| Interfacing Sensors & Transducers to Data Acquisition Systems in which Large Common Mode Signals are |         |

| Present                                                                                              | 190-195 |

| Consider the JFET When you Have a Priority Performance Objective                                     | 196-202 |

| Linear Systems' LSK489 Application Note                                                              | 203-219 |

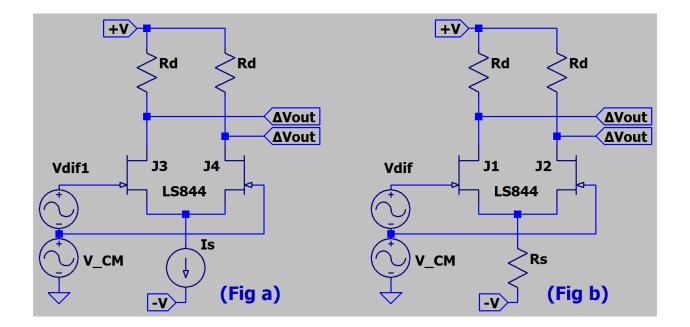

| LS844 Application Note                                                                               | 220-236 |

| Comparison of Important Design Specs for JFETs Used in Small Signal Applications                     | 237-243 |

| A Guide to Using FETs for Sensor Applications                                                        |         |

| Higher Performance Military Sensor Signal Chains                                                     |         |

| Linear Systems' J201 High Gain N-CH JFET                                                             |         |

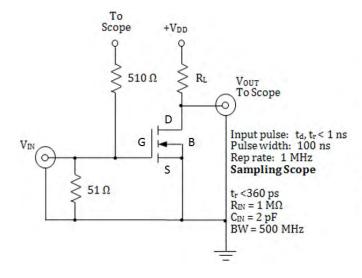

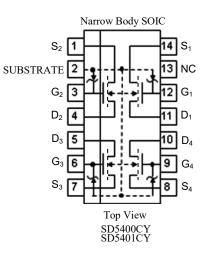

| High-Speed DMOS FET Analog Switches and Switch Arrays                                                |         |

| Applications for Low Leakage Diodes                                                                  |         |

| Linear Systems' Current Regulating Diodes                                                            |         |

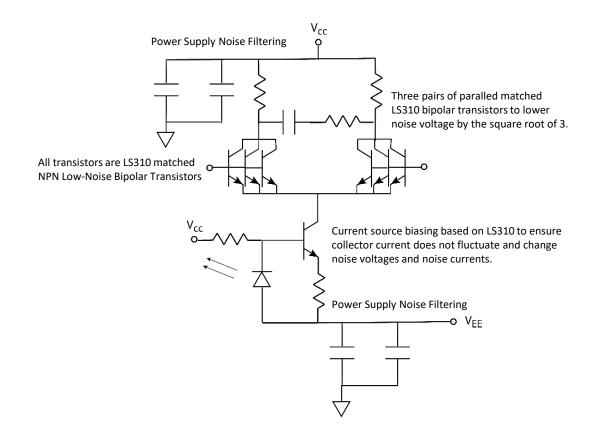

| Solving the Noise Puzzle with Low-Noise Matched Bipolar Transistor Pairs - LS310 & LS350             |         |

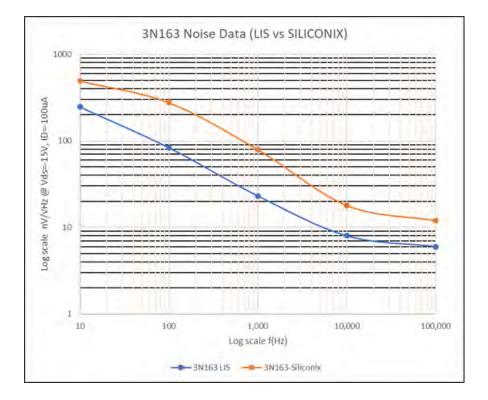

| Radiation Sensor Design and Applications, The 3N163                                                  |         |

| A Guide to Using FETs for Voltage Controlled Circuits                                                |         |

# Linear Systems' 2024 Data Book

# Testimonials

"One of the main reasons we offer a lifetime warranty for our products is because we can count on Linear Systems. The Linear Systems' LSK389B J-FET is so reliable that in the rare event a faulty unit is discovered, it's the very last variable we check. The LSK389B J-FET simply doesn't fail!"

Rodger Cloud www.cloudmicrophones.com

"I believe that selecting Linear Systems' LSJ74 for our Halo Integrated Amplifier has contributed to the unprecedented number of rave reviews and awards it's received. Parasound's product development team commends Linear Systems for providing customer support that is top-notch."

#### **Richard Schram**

www.parasound.com

"Our QCL instrument has the lowest noise commercially available and is used for pharmaceutical process quality control and trace gas emissions monitoring. Noise testing the instrument is critical to ensuring performance. Our test equipment uses the Linear Systems' LSK389 JFET. The precision of the LSK389 makes verifying the precision of our instruments possible."

#### Lisa Mueller

www.teamwavelength.com

# Introduction

Welcome to the 2024 edition of the Linear Systems Data Book. Here we present all our devices in one single document to give you a complete overview of our portfolio. We hope that makes it even easier for you to find the right product for your design. Our extensive portfolio offers high-quality discrete components serving a wide range of markets including automated test equipment, professional audio, medical electronics, military and test & measurement. Our products are housed in some of the most advanced, industry-leading small packages, as well as robust industry standard packages giving designers many options. Alongside quality and efficiency, Linear Systems' customers value reliability and a constant supply they can trust. We produce consistently reliable discrete components and we work at every step to safeguard the long-term availability of our manufacturing processes and products, to ensure secure supply for all our customers. In addition, Linear Systems has an on-site testing facility to conduct a full range of production and post-production testing. Specialized capabilities include: Hi-temperature product testing and the highest capacity sub-nanovolt noise production testing capability in the world. We have a long history in the business and broad range of experience. Linear Systems ensures dedicated in-house technical support – from simplifying selection via quick-reference material to in-person technical meetings with our engineering team. All to help you choose the best devices for the most efficient design.

This Data Book provides all Linear Systems' datasheets in one spot. The Table of Contents includes product category, part number and part description, so you can browse the entire product line with ease. There is also a dedicated section on packages, highlighting the latest package innovations and packing options.

# **Ordering Information and Sampling Policy**

Linear Systems does not impose minimum order requirements when ordering directly from the factory. We understand customers may only need a few parts for prototyping, repairs, student projects or DIY designs. Our parts are available to all. We do, however, offer incremental price breaks for increased purchase quantity. Linear Systems also supports customers who require very large quantities for mass production. In this case special high-quantity pricing may be negotiated for bulk purchases of 100,000 plus pieces.

Do you use the LTspice<sup>®</sup> electronic circuit simulator? The majority of Linear Systems' parts are included in the latest edition of the LTspice<sup>®</sup> embedded library. Customers often try our products through the <u>Allspice-simulator</u> before ordering.

Would you like to receive samples? Samples including detailed data logs are available upon request.

Interested in a part not listed on our website, or do you need a custom part? Linear Systems offers many non-standard electrical screening and package options.

Linear Systems' friendly staff are here to help. For any kind of assistance you can reach us by calling (510) 490-9160 or email us at <a href="mailto:support@linearsystems.com">support@linearsystems.com</a>.

# **Our Commitment:**

# **Quality and Reliability**

**Quality is Everything**

Linear Systems is ISO 9001:2015 certified. All our processes and manufacturing facilities are subject to regular internal audits.

#### **Continuously Improve**

Linear Systems' Continuous Improvement Program (CIP) ensures that existing processes are strategically reviewed while each new development builds on past learning. The result is that best practices are always employed.

Zero defect is our goal. To ensure continuous improvement, failure analysis and the determination to find root causes is performed at all stages of development and production by adoption of quality-analysis tools and methods.

# DISCRETE COMPONENT PRODUCT LINE

# LSK389 A/B/C/D

Over 30 Years of Quality Through Innovation

Ultra-Low Noise Monolithic Dual N-Channel JFET Amplifier

# **INDUSTRY'S FIRST 100% TESTED LOWEST NOISE JFET**

| Absolute Maximum Ratings             |                          |  |  |  |  |  |  |  |

|--------------------------------------|--------------------------|--|--|--|--|--|--|--|

| @ 25 °C (unless otherwise stated)    |                          |  |  |  |  |  |  |  |

| Maximum Temperatures                 |                          |  |  |  |  |  |  |  |

| Storage Temperature                  | -65 to +150°C            |  |  |  |  |  |  |  |

| Junction Operating Temperature       | -55 to +150°C            |  |  |  |  |  |  |  |

| Maximum Power Dissipation            |                          |  |  |  |  |  |  |  |

| Continuous Power Dissipation @ +25°C | 400mW                    |  |  |  |  |  |  |  |

| Maximum Currents                     |                          |  |  |  |  |  |  |  |

| Gate Forward Current                 | I <sub>G(F)</sub> = 10mA |  |  |  |  |  |  |  |

| Maximum Voltages                     | Maximum Voltages         |  |  |  |  |  |  |  |

| Gate to Source                       | $V_{GSS} = 40V$          |  |  |  |  |  |  |  |

| Gate to Drain                        | $V_{GDS} = 40V$          |  |  |  |  |  |  |  |

#### Features

- Ultra-Low Noise:  $e_n = 1.3 nV/\sqrt{Hz}$ (typ), f = 1.0 kHz and NBW = 1.0 Hz

- Ultra-Low Noise:  $1.5 \text{nV}/\sqrt{\text{Hz}}$  (typ), f = 10Hz and NBW = 1.0Hz

- Tight Matching:  $IV_{GS1-2}I = 15mV max$

- High Breakdown Voltage: BV<sub>GSS</sub> = 40V max

- High Gain:  $G_{fs} = 20mS$  (typ)

- Low Capacitance: 25pF (typ)

- Improved Second Source Replacement for 2SK389

#### **Benefits**

- Improved System Noise Performance

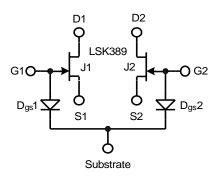

- Unique Monolithic Dual Design Construction of Interleaving Both JFETs on the Same Piece of Silicon

- **Excellent Matching and Thermal** Tracking

- Great for Maximizing Battery Operated Applications by Providing a Wide Output Swing

- A High Signal to Noise Ratio as a Result of the LSK389's Low and **Tightly Matched Gate Threshold** Voltages

#### Applications

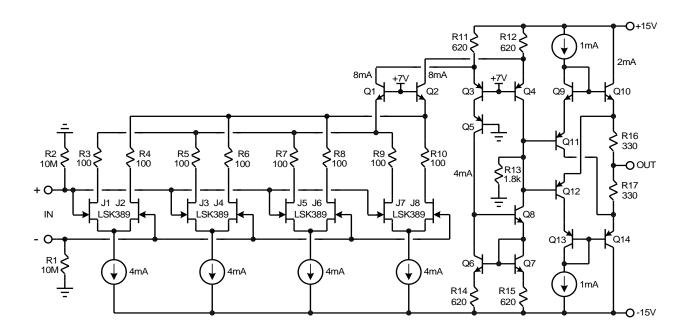

- Audio Amplifiers and Preamps

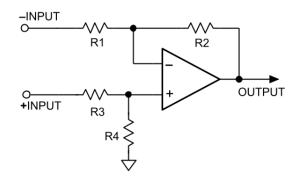

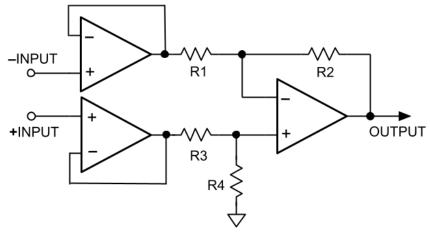

- **Discrete Low-Noise Operational** Amplifiers

- **Battery-Operated Audio Preamps**

- Audio Mixer Consoles

- Acoustic Sensors

- Sonic Imaging

- Instrumentation Amplifiers

- Microphones

- Sonobouys

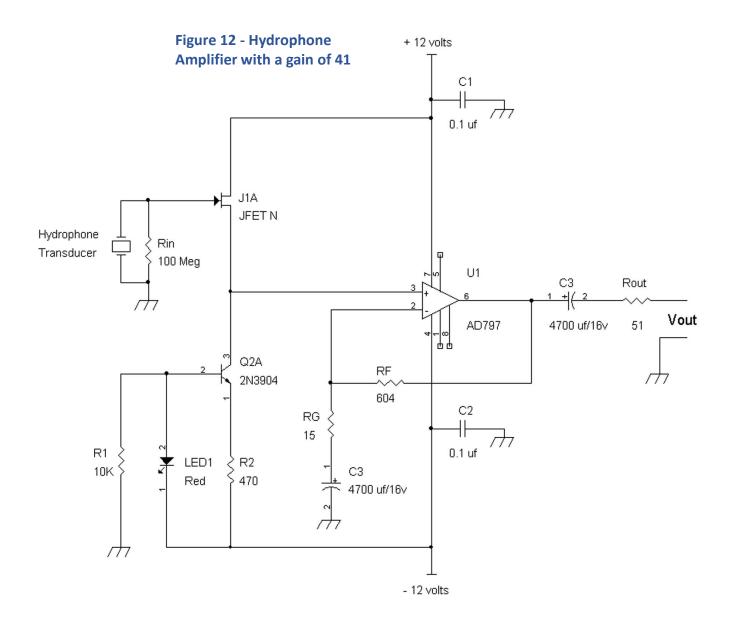

- Hvdrophones

- **Chemical and Radiation Detectors**

#### Description

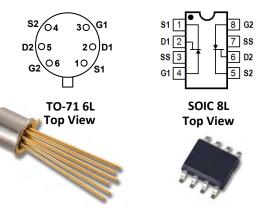

Channel JFET, 100% tested, guaranteed to meet 1/f and broadband noise specifications, while eliminating burst (RTN or popcorn) noise entirely. The LSK389 Series, Monolithic Dual N-Channel JFETs were specifically designed to provide users a better performing, less time consuming and cheaper solution for obtaining tighter IDSS matching, and better thermal tracking, than matching individual JFETs. The LSK389's features incorporate four grades of IDSS: 2.6-6.5mA, 6.0-12.0mA, 10.0percent, a gate threshold offset of 15mV, a voltage noise (en) of  $1.3 \text{nV}/\sqrt{\text{Hz}}$  typical at f = 1.0kHZ, with a Gain LSK389 provides a wide output swing, and a high signal version, please refer to the LSK170 datasheet.

The LSK389 is the industry's lowest noise Dual N- to noise ratio as a result of the LSK389's tightly matched and low gate threshold voltages. The 40V breakdown provides maximum linear headroom in high transient program content amplifiers.

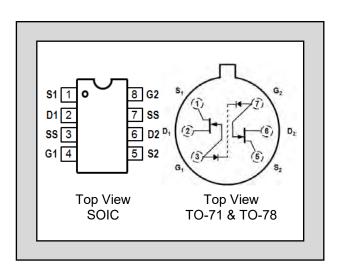

Additionally, the LSK389 provides a low input noise to capacitance product that has nearly zero popcorn noise. The narrow ranges of the IDSS electrical grades combined with the superior matching performance of the LSK389's monolithic dual construction promote ease of device tolerance in low voltage applications, as compared 20.0mA and 17-30mA, with an IDSS match of 10 to matching single JFETs. Available in surface mount SOIC 8L and thru-hole TO-71 6L packages.

Contact the factory for tighter noise and other of 20mS typical, and 25pF of capacitance typical. The specification selections. For equivalent single N-Channel

| SYMBOL               | CHARACTERISTIC                      |         |      | TYP  | MAX  | UNITS  | CONDITIONS                                                   |

|----------------------|-------------------------------------|---------|------|------|------|--------|--------------------------------------------------------------|

| BV <sub>GSS</sub>    | Gate to Source Breakdown Vo         | ltage   | -40  |      | 1    | V      | $V_{DS} = 0, I_D = -100 \mu A$                               |

| V <sub>GS(OFF)</sub> | Gate to Source Pinch-off Volta      | ge      | -0.3 |      | -1.6 | V      | $V_{DS} = 10V, I_D = 0.1 \mu A$                              |

|                      |                                     | LSK389A | 2.6  |      | 6.5  |        |                                                              |

|                      | Drain to Source Saturation          | LSK389B | 6    |      | 12   |        | $V_{DS} = 10V. V_{CS} = 0$                                   |

| IDSS                 | Current                             | LSK389C | 10   |      | 20   | mA     | $v_{\rm DS} = 10v, v_{\rm GS} = 0$                           |

|                      |                                     | LSK389D | 17   |      | 30   |        |                                                              |

| I <sub>GSS</sub>     | Gate to Source Leakage Current      |         |      | -100 | -300 | pА     | $V_{GS} = -25V, V_{DS} = 0$                                  |

| $I_{G1G2}$           | Gate to Gate Isolation Current      |         |      | ±1.0 | ±50  | nA     | $V_{G1^-G2} = \pm 45V, I_D = I_S = 0A$                       |

| G <sub>fs</sub>      | Full Conduction Transconducta       | ance    | 8    | 20   | 1    | mS     | $V_{DS} = 10V, V_{GS} = 0, f = 1kHz$                         |

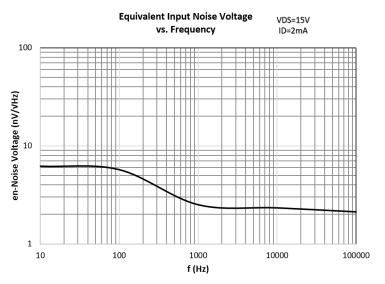

| e <sub>n</sub>       | Noise Voltage                       |         |      | 1.3  | 1.9  | nV/√Hz | $V_{DS}$ = 10V, $I_D$ = 2mA, $f$ = 1kHz,<br>NBW = 1Hz        |

| en                   | Noise Voltage                       |         |      | 1.5  | 4.0  | nV/√Hz | $V_{DS}$ = 10V, $I_D$ = 2mA, $f$ = 10Hz,<br>NBW = 1Hz        |

| C <sub>ISS</sub>     | Common Source Input Capacitance     |         |      | 25   |      | pF     | V <sub>DS</sub> = 10V, V <sub>GS</sub> = 0, <i>f</i> = 1MHz, |

| C <sub>RSS</sub>     | Common Source Reverse Transfer Cap. |         |      | 5.5  |      | pF     | $V_{DG} = 10V, I_{D} = 0, f = 1MHz,$                         |

#### Electrical Characteristics @ 25°C (unless otherwise stated)

#### Matching Characteristics @ 25°C (unless otherwise stated)

| SYMBOL    | CHARACTERISTIC                             | MIN | TYP | MAX | UNITS | CONDITIONS                                  |

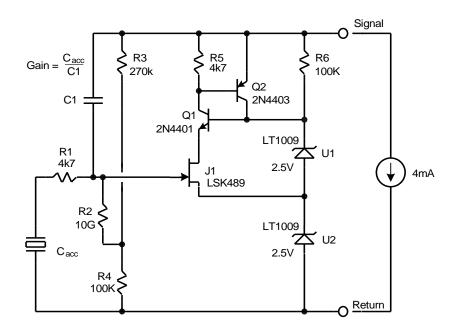

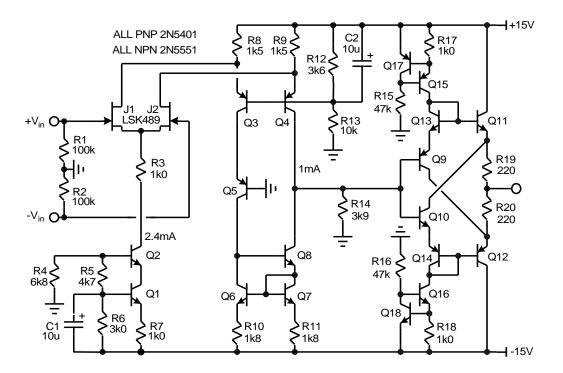

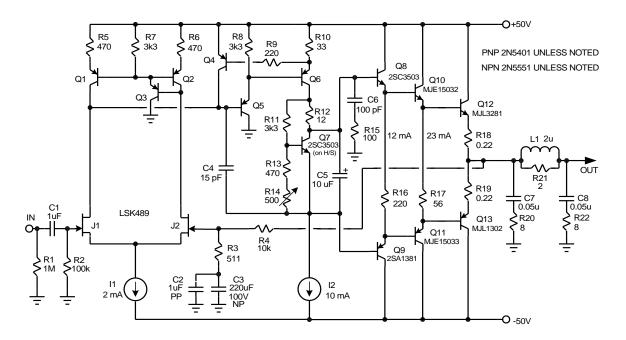

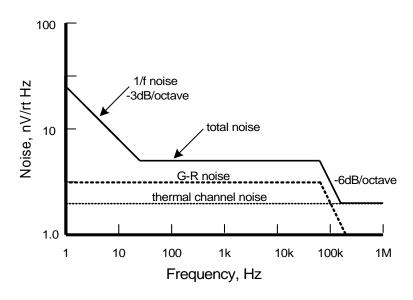

|-----------|--------------------------------------------|-----|-----|-----|-------|---------------------------------------------|

| VGS1-VGS2 | Differential Gate to Source Cutoff Voltage |     | 6.0 | 15  | mV    | V <sub>DS</sub> = 10V, I <sub>D</sub> = 1mA |

|           | Saturation Drain Current Ratio             | 0.9 | 1.0 | 1.1 | n/a   | V <sub>DS</sub> = 10V, V <sub>GS</sub> = 0V |

#### Notes

1. Absolute maximum ratings are limiting values above which serviceability may be impaired.

2. Pulse Test: PW  $\leq$  300µs, Duty Cycle  $\leq$  3%

3. All characteristics MIN/TYP/MAX numbers are absolute values. Negative values indicate electrical polarity only.

Information furnished by Linear Integrated Systems is believed to be accurate and reliable. However, no responsibility is assumed for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Linear Integrated Systems.

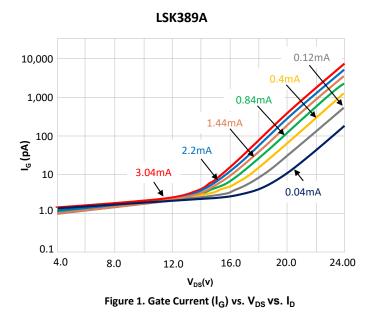

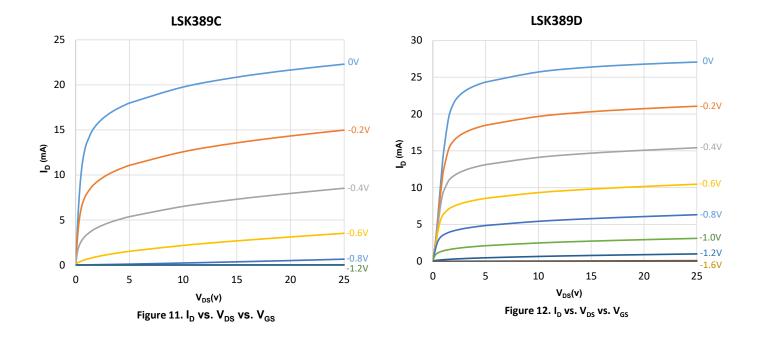

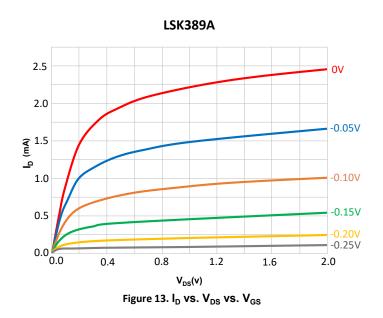

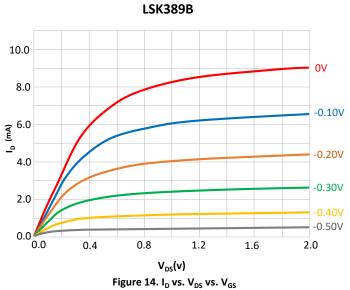

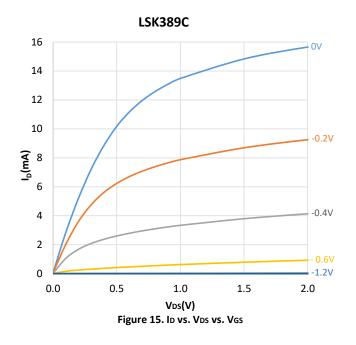

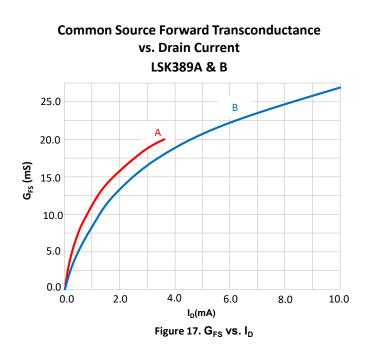

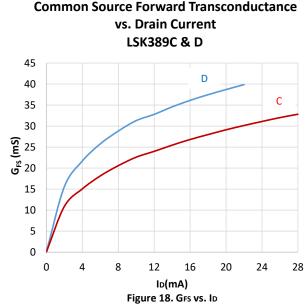

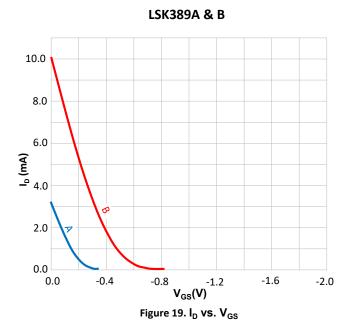

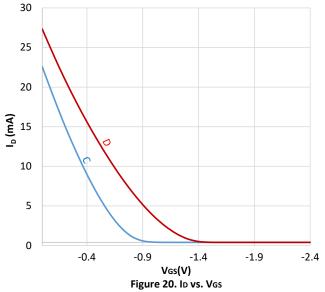

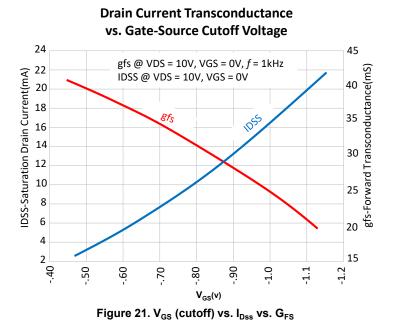

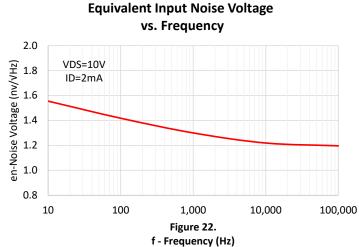

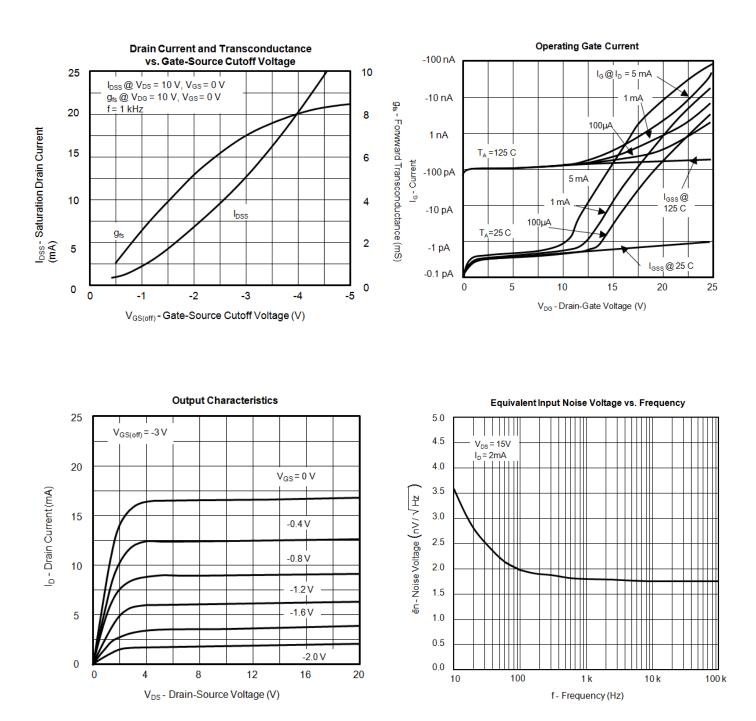

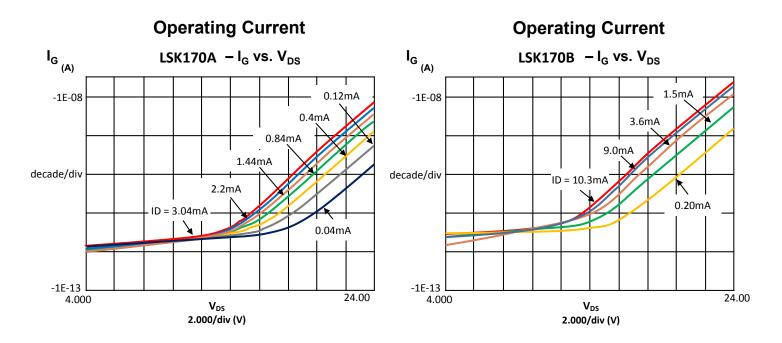

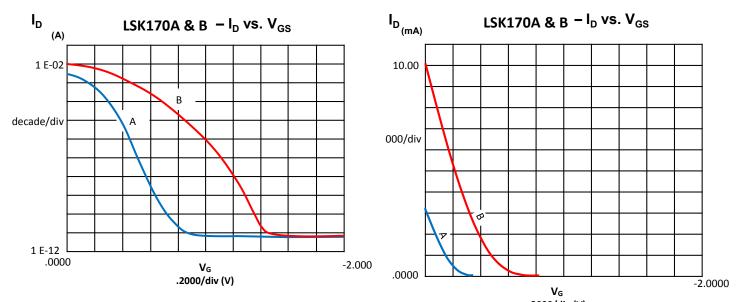

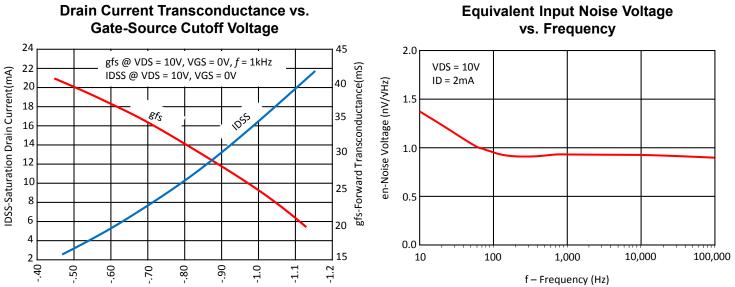

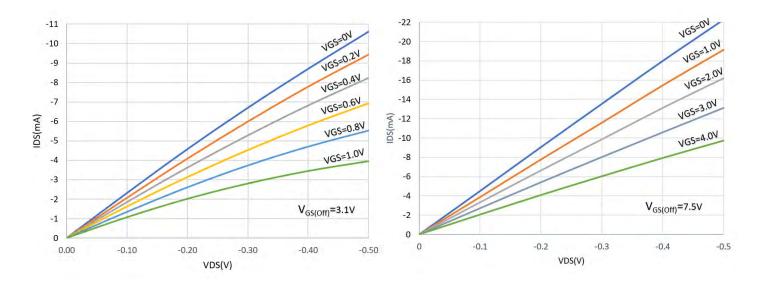

## **Typical Characteristics**

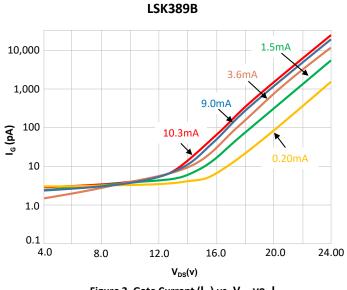

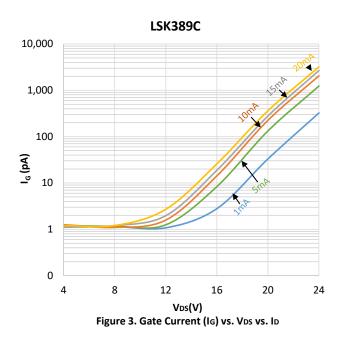

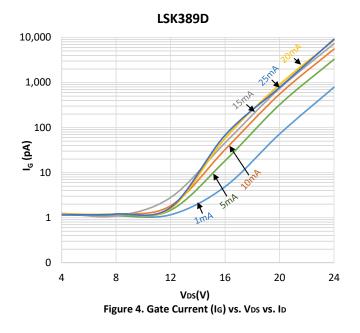

Figure 2. Gate Current (I<sub>G</sub>) vs. V<sub>DS</sub> vs. I<sub>D</sub>

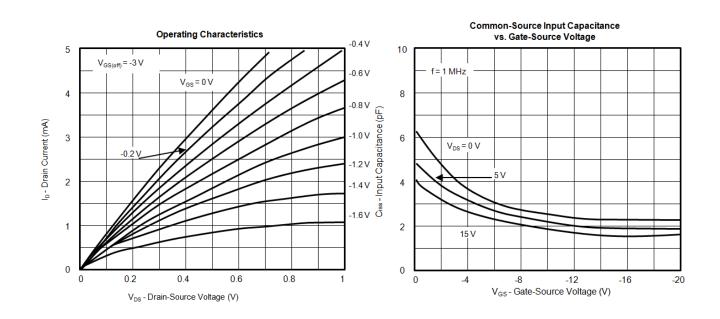

## **Typical Characteristics Continued**

LSK389B

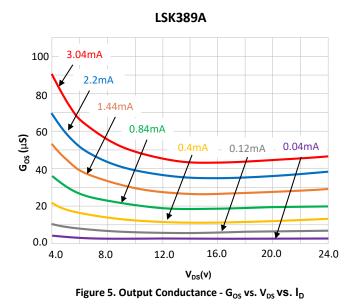

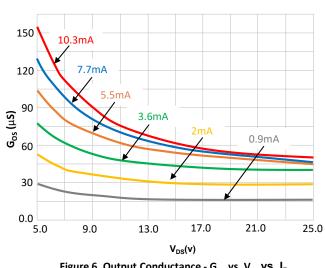

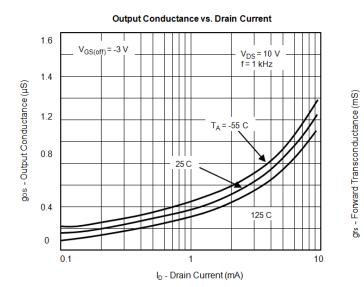

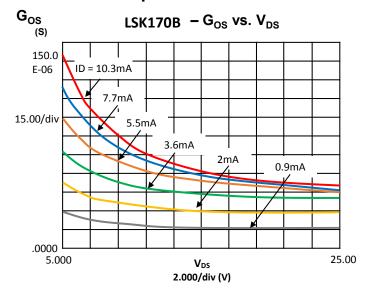

Figure 6. Output Conductance - G<sub>os</sub> vs. V<sub>DS</sub> vs. I<sub>D</sub>

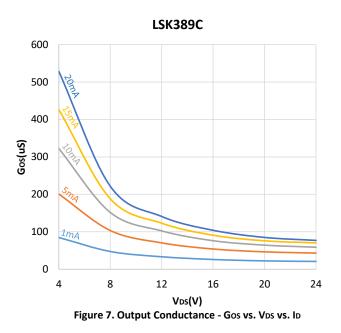

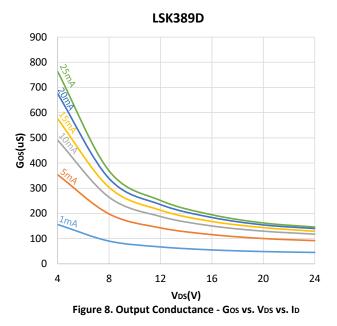

## **Typical Characteristics Continued**

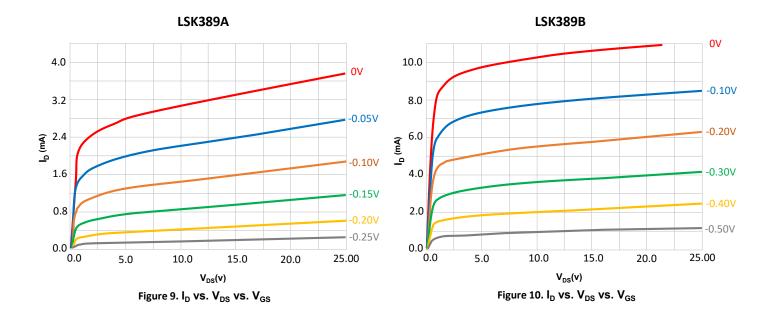

LSK389D 22 0V 20 18 - 0.2V 16 14 (**4** 12 10 10 - 0.4V 8 6 4 0.8V 2 - 1.0V - 1.2V - 1.6V 2.0 0 0.5 0.0 1.0 1.5 VDS(V) Figure 16. ID vs. VDs vs. VGS

## **Typical Characteristics Continued**

LSK389C & D

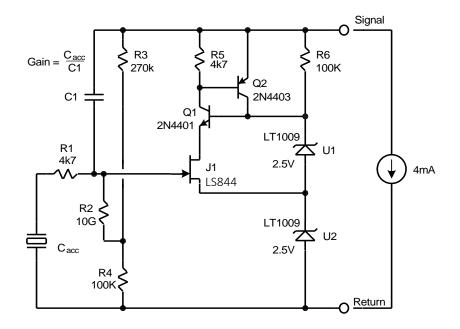

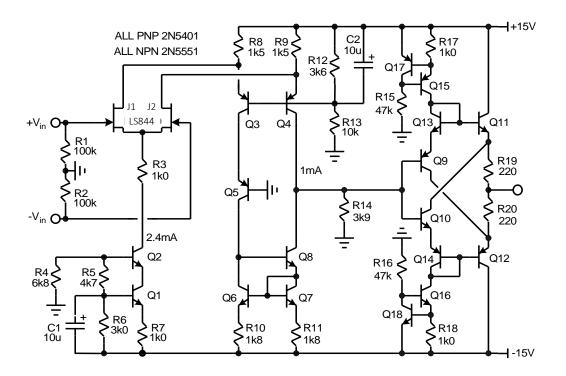

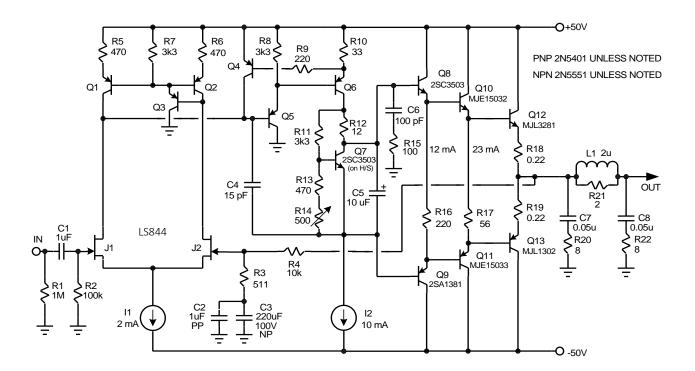

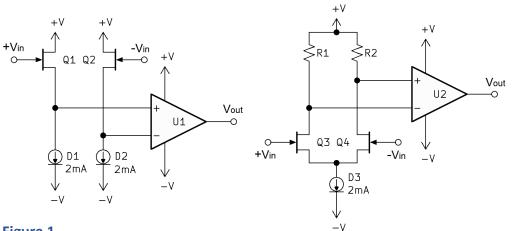

**Common Source Forward Transconductance**

### **Typical Characteristics**

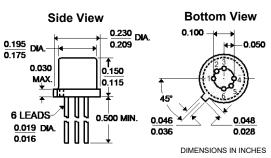

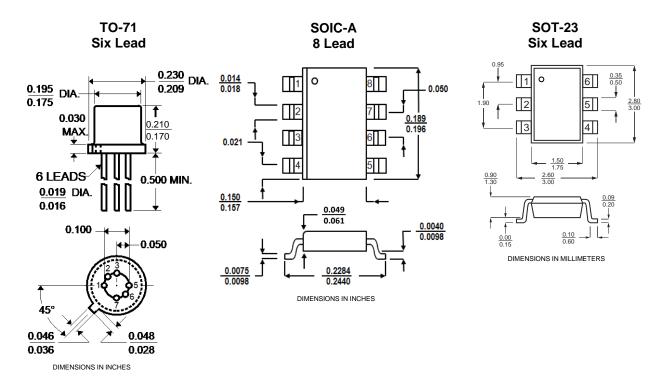

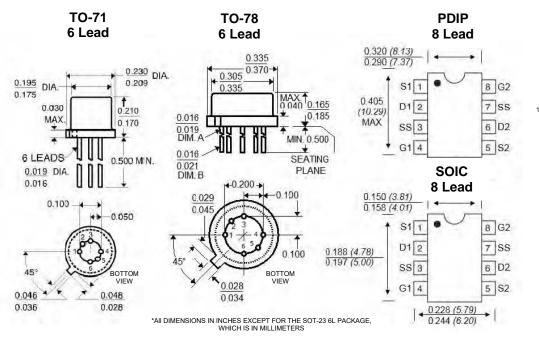

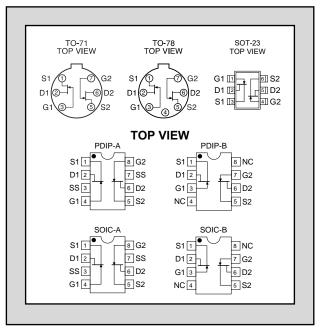

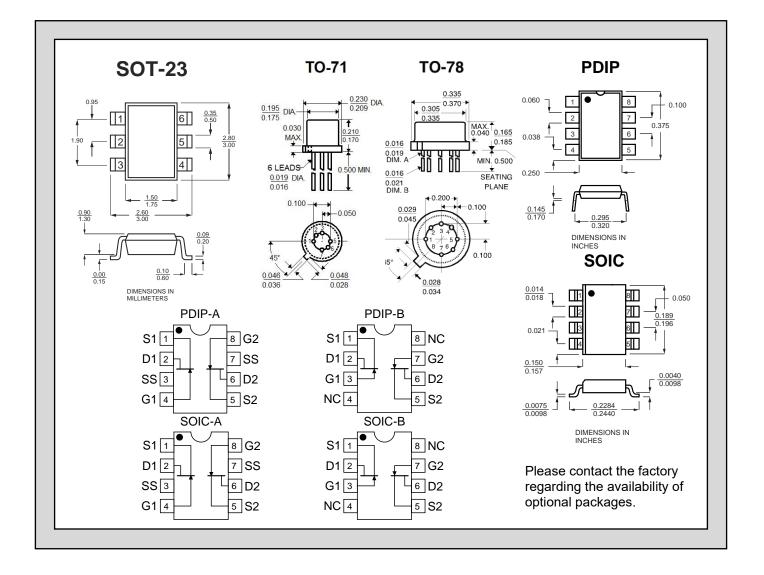

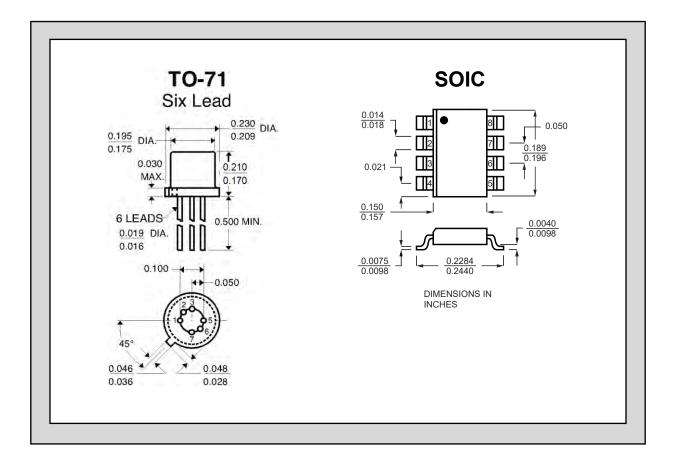

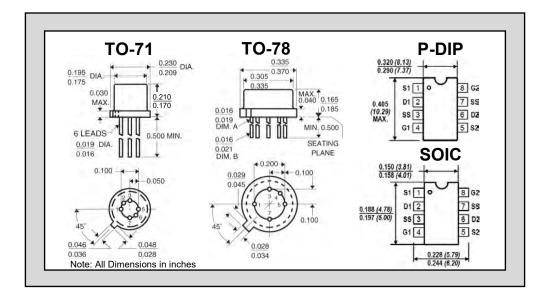

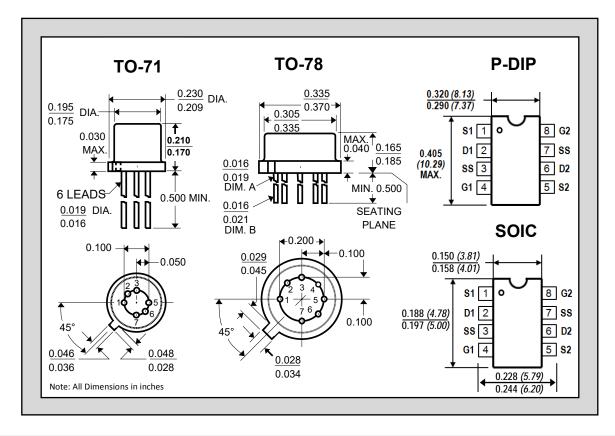

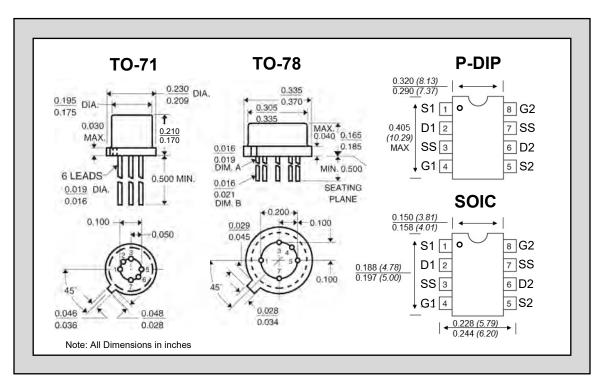

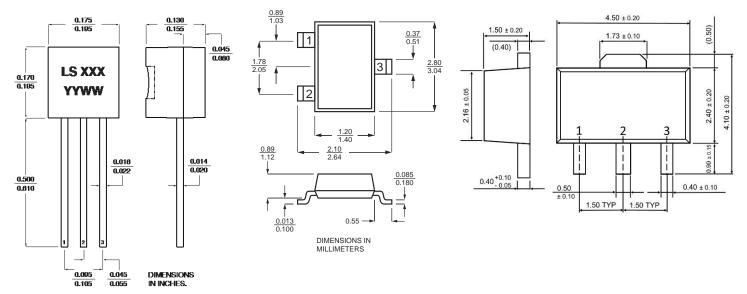

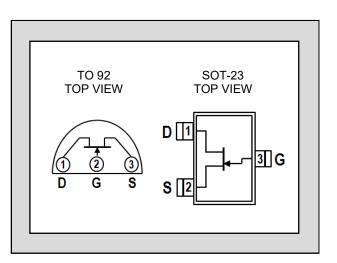

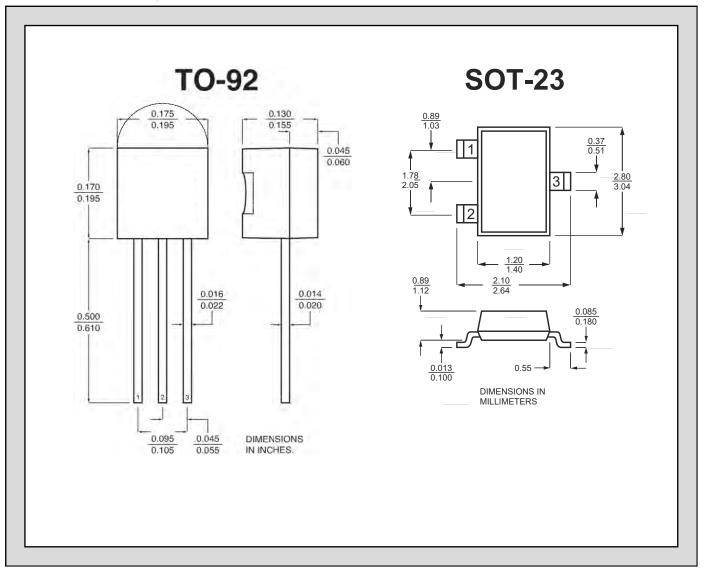

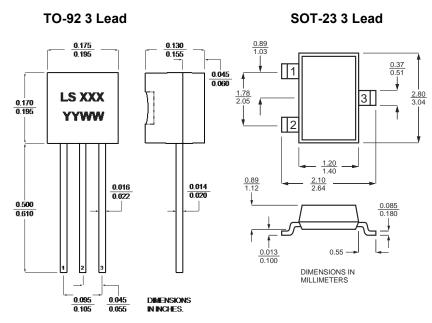

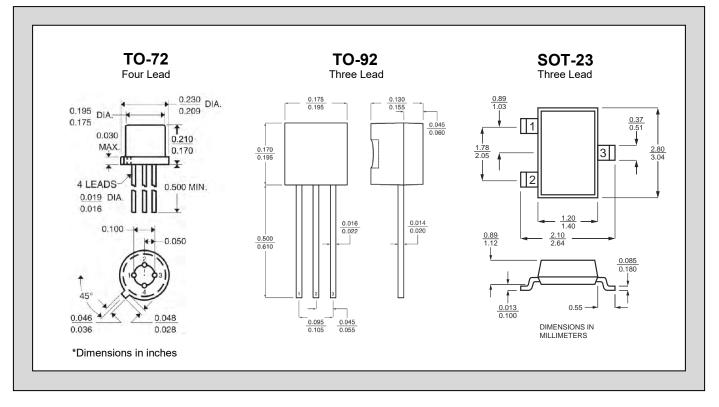

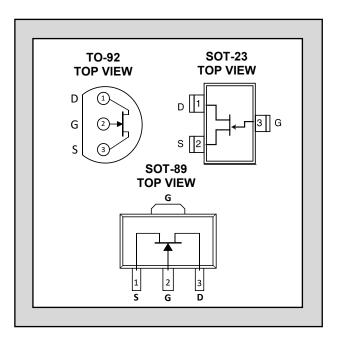

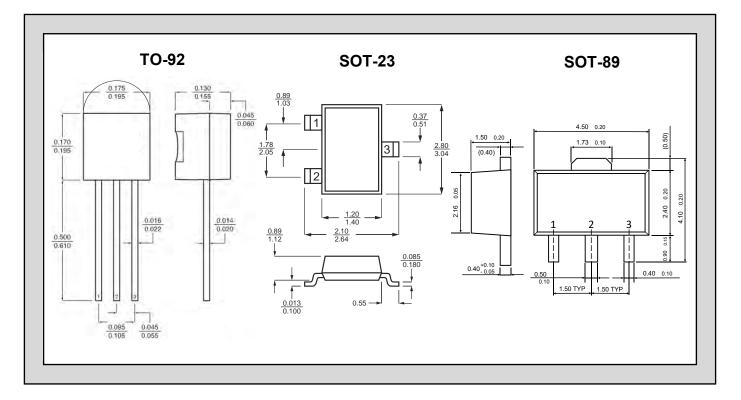

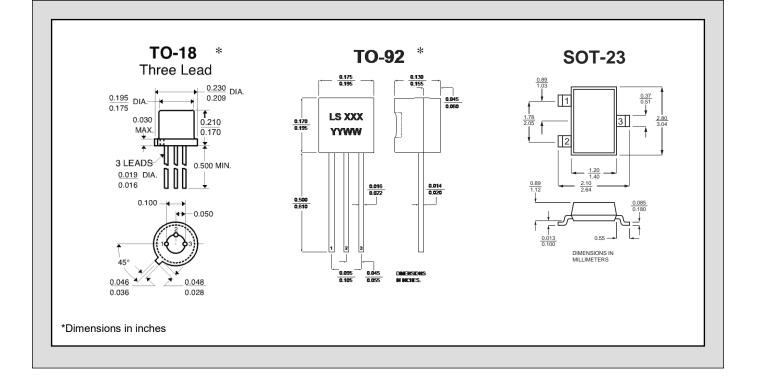

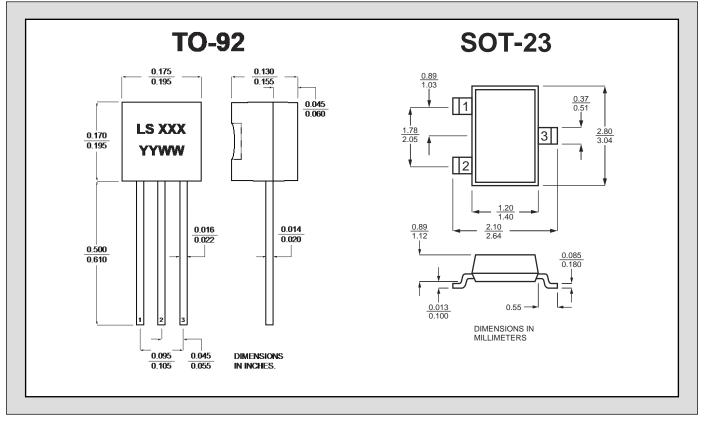

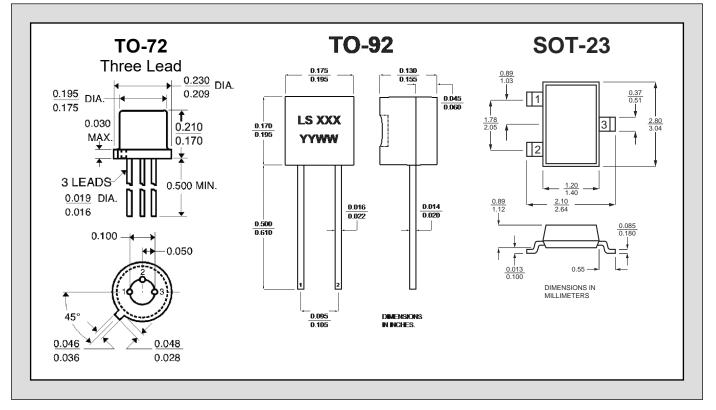

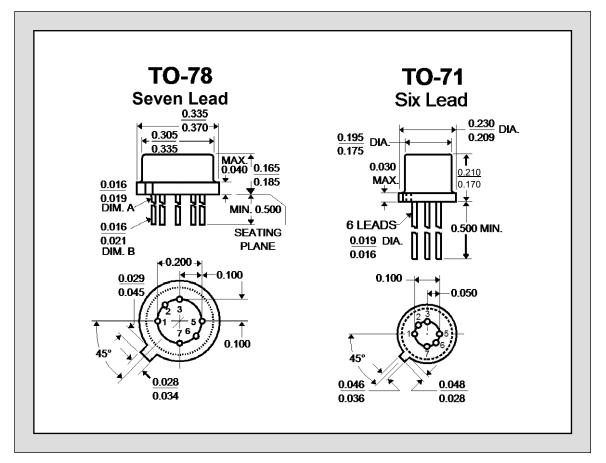

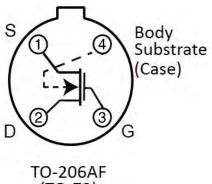

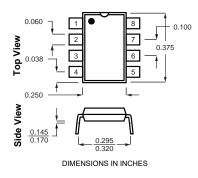

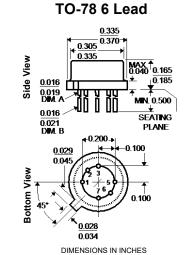

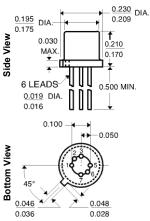

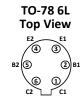

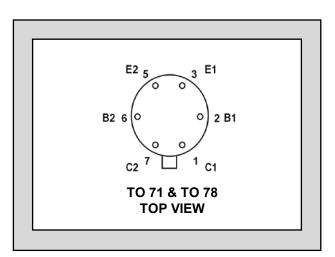

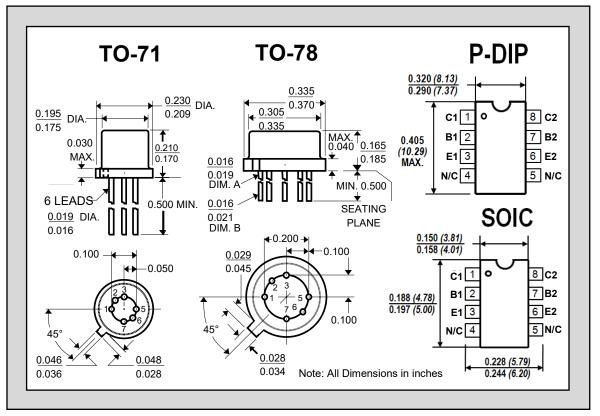

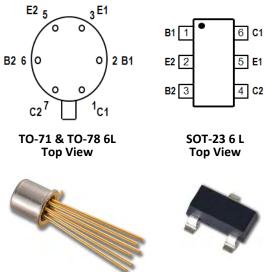

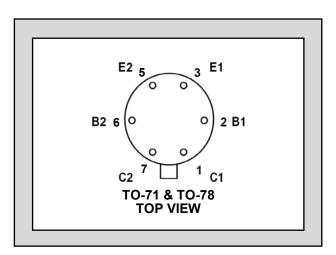

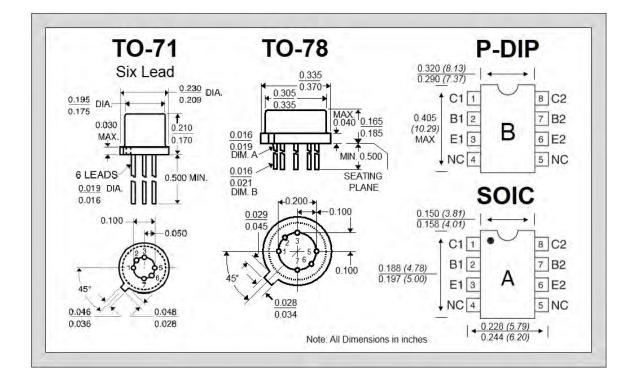

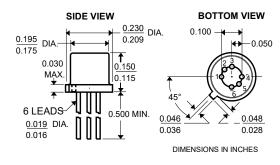

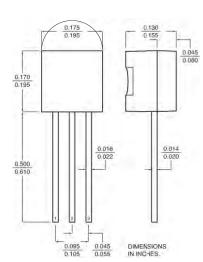

#### **Package Dimensions**

#### TO-71 6 Lead

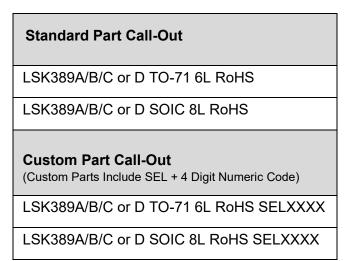

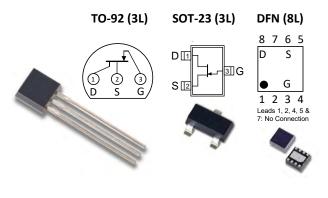

## **Ordering Information**

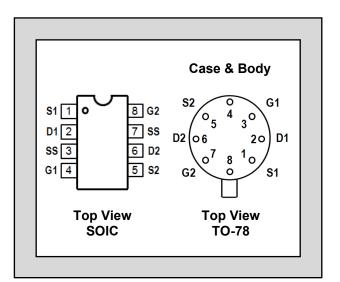

SS: SUBSTRATE, LEAVE THESE PINS FLOATING (N/C)

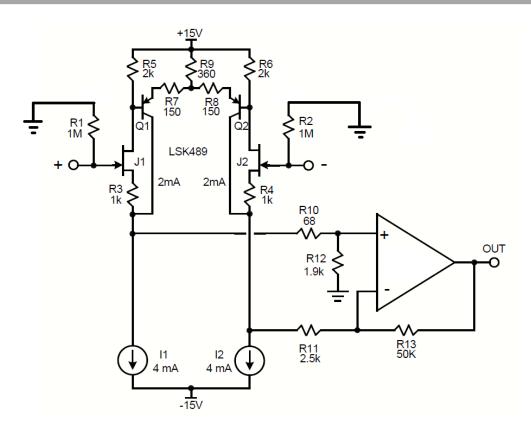

# LSK489A/B

Over 30 Years of Quality Through Innovation

**NEAR SYSTEM**

Low Noise, Monolithic Dual N-Channel JFET Amplifier

#### INDUSTRY'S LOWEST INPUT CAPACITANCE MONOLITHIC DUAL N-CHANNEL JFET

| Absolute Maximum Ratings                            |                                      |  |  |  |  |  |  |  |  |

|-----------------------------------------------------|--------------------------------------|--|--|--|--|--|--|--|--|

| @ 25 °C (unless otherwise stated)                   |                                      |  |  |  |  |  |  |  |  |

| Maximum Temperatures                                |                                      |  |  |  |  |  |  |  |  |

| Storage Temperature                                 | -55 to +150°C                        |  |  |  |  |  |  |  |  |

| Junction Operating Temperature                      | -55 to +150°C                        |  |  |  |  |  |  |  |  |

| Maximum Power Dissipation, TA = 25°C                | Maximum Power Dissipation, TA = 25°C |  |  |  |  |  |  |  |  |

| Continuous Power Dissipation, per side <sup>4</sup> | 300mW                                |  |  |  |  |  |  |  |  |

| Power Dissipation, total <sup>5</sup>               | 500mW                                |  |  |  |  |  |  |  |  |

| Maximum Currents                                    |                                      |  |  |  |  |  |  |  |  |

| Gate Forward Current                                | $I_{G(F)} = 10 \text{mA}$            |  |  |  |  |  |  |  |  |

| Maximum Voltages                                    |                                      |  |  |  |  |  |  |  |  |

| Gate to Source                                      | $V_{GSS} = 60V$                      |  |  |  |  |  |  |  |  |

| Gate to Drain                                       | $V_{GDS} = 60V$                      |  |  |  |  |  |  |  |  |

| Features                                            |                                      |  |  |  |  |  |  |  |  |

| Low Noise (f = 1kHz, NBW = 1Hz)                     | e <sub>n</sub> = 1.8nV/√Hz           |  |  |  |  |  |  |  |  |

| Low Input Capacitance                               | Ciss = 4pF                           |  |  |  |  |  |  |  |  |

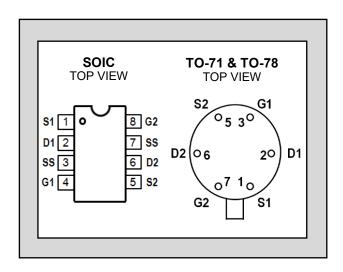

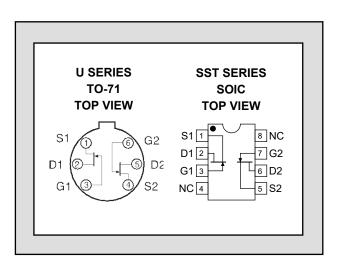

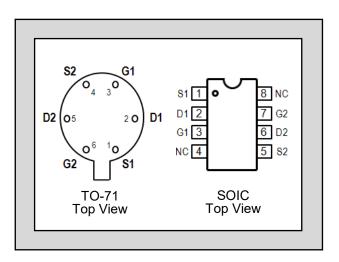

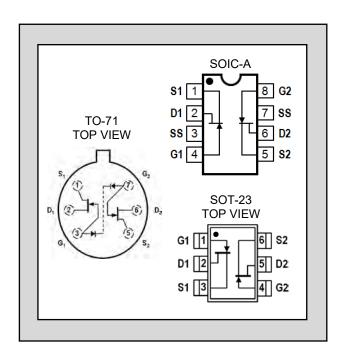

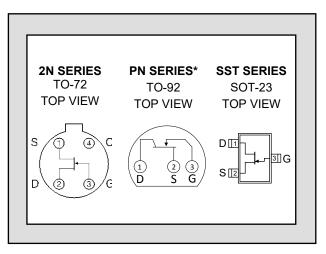

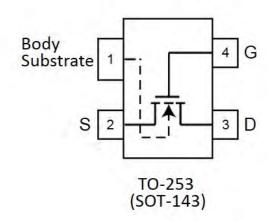

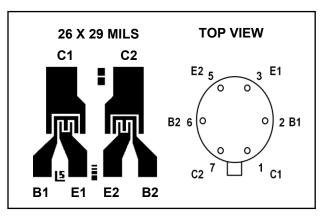

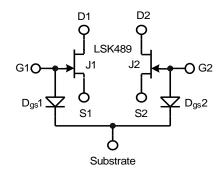

**S**2 G1 0<sub>5 3</sub>0 **S1** G2 6 S2 G1 [[1 SS D1 2 D1 D2 20 06 D1 2 5 D2 6 D2 SS 3 S1 [] 4 G2 G1 4 5 S2 SOIC-A SOT-23 TO-71 **Top View Top View Top View** \* For equivalent single version, see LSK189

#### Features

- Low Noise: en = 1.8nV/√Hz (typ), f = 1kHz, NBW = 1Hz

- Very Low Common Source Input Capacitance of C<sub>ISS</sub> = 4pF - typ

- High Slew Rate

- Low Offset/Drift Voltage

- Low Gate Leakage IGSS and IG

- High CMRR 102 dB

#### Benefits

- Tight Differential Voltage Match vs. Current

- Improved Op Amp Speed Settling Time Accuracy

- Minimum Input Error Trimming Error Voltage

- Lower Intermodulation Distortion Due to Low Input Capacitance

#### Applications

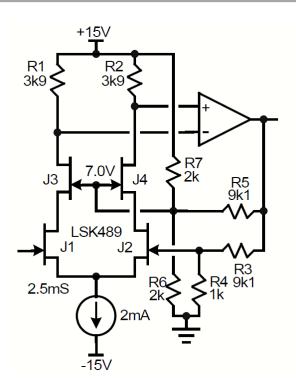

- Wideband Differential Amplifiers

- High Speed Temperature Compensated Single Ended Input Amplifier

- High Speed Comparators

- Impedance Converters

- Sonobouys and Hydrophones

- Acoustic Sensors

#### Description

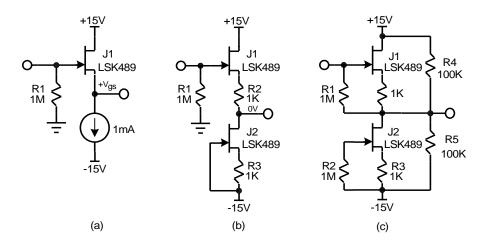

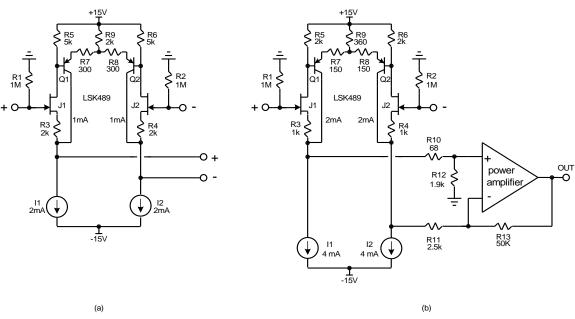

The LSK489 is the industry's lowest input capacitance and low-noise monolithic dual N-Channel JFET. Low input capacitance substantially reduces intermodulation distortion. In addition, these dual JFETs feature tight offset voltage and low drift over temperature range, and are targeted for use in a wide range of precision instrumentation and sensor applications. The LSK489 is available in surface mount plastic SOIC 8L and SOT-23 6L, as well as thru-hole metal TO-71 6L packages. For an equivalent single N-Channel version refer to the LSK189 datasheet. LSK489 TO-71 6L and SOIC 8L are fit, form and pin compatible to the same LSK389 product.

The LSK489 provides a dramatic increase in capabilities for a wide range of low-noise applications. The most significant aspect of the LSK489 is how it combines a noise level nearly as low as the LSK389 while having much lower gate-to-drain capacitance, 4pF versus the 25pF. The slightly higher noise of the LSK489, versus the LSK389, is not significant in most instances, while the much lower capacitance enables designers to produce simpler, more elegant circuit designs with fewer devices that cost less in production. Also notice that the LSK489 and LSK389 TO-71 and SOIC packages are the same and pin compatible, therefore, they can be used interchangeably.

Like the Linear Systems LSK389, the LSK489 features a unique design construction of interleaving both JFETs on the same piece of silicon to provide excellent matching and thermal tracking, as well a low-noise profile having nearly zero popcorn noise. I<sub>DSS</sub> range is divided into two segments providing designers improved resolution, which are A grade ( $\Delta$ I<sub>DSS</sub> = 6mA) and B grade ( $\Delta$ I<sub>DSS</sub> = 7mA). Contact Linear Systems for improved En, I<sub>DSS</sub>, V<sub>GS</sub>(off),  $\Delta$  V<sub>GS</sub> or any other limits. Based on new limits, LS will assign a new SELXXXX code to be used in shipments.

#### LSK489A/B

| Symbol         | Characteristic                                                                      | Min. | Тур. | Max | Units  | Conditions                                                     |

|----------------|-------------------------------------------------------------------------------------|------|------|-----|--------|----------------------------------------------------------------|

| VGS1-VGS2      | Differential Gate to Source Cutoff Voltage                                          | -    | 8    | 20  | mV     | $V_{DS} = 10V, I_D = 1mA$                                      |

| IDSS1<br>IDSS2 | Gate to Source Saturation Current Ratio                                             | 0.9  | -    | 1.0 | -      | $V_{DS}=10V,V_{GS}=0V$                                         |

| CMRR           | <u>Common Mode Rejection Ratio</u><br>-20 log ΔV <sub>GS1-2</sub> /ΔV <sub>DS</sub> | 95   | 102  | -   | dB     | $V_{DS}$ = 10V to 20V, $I_D$ = 200 $\mu A$                     |

| en             | Noise Voltage                                                                       | -    | 1.8  | -   | nV/√Hz | $V_{DS} = 15V$ , $I_D = 2.0$ mA, $f = 1$ kHz,<br>NBW = 1Hz     |

| en             | Noise Voltage                                                                       | -    | 3.5  | -   | nV/√Hz | $V_{DS} = 15V, I_D = 2.0mA, f = 10Hz, NBW = 1Hz$               |

| Ciss           | Common Source Input Capacitance                                                     | -    | 4    | -   | pF     |                                                                |

| Crss           | Common Source Reverse Transfer<br>Capacitance                                       | -    | 2    | -   | pF     | V <sub>DS</sub> = 15V, I <sub>D</sub> = 500μA, <i>f</i> = 1MHz |

#### Matching Characteristics @ 25°C (unless otherwise stated)

#### Electrical Characteristics @ 25°C (unless otherwise stated)

| Symbol            | Characteristic                    |            |      | Тур. | Max  | Units | Conditions                                                                |

|-------------------|-----------------------------------|------------|------|------|------|-------|---------------------------------------------------------------------------|

| BV <sub>GSS</sub> | Gate to Source Breakdow           | vn Voltage | -60  | -    | -    | V     | $V_{DS} = 0, I_D = -1nA$                                                  |

| V(BR)G1 - G2      | Gate to Gate Breakdown            | Voltage    | ±30  | ±45  | -    | V     | I <sub>G</sub> = ±1µA, I <sub>D</sub> =I <sub>S</sub> =0 A (Open Circuit) |

| $V_{GS(OFF)}$     | Gate to Source Pinch-off          | Voltage    | -1.5 | -    | -3.5 | V     | $V_{DS} = 15V, I_D = 1nA$                                                 |

| Vgs               | Gate to Source Operating          | g Voltage  | -0.5 | -    | -3.5 | V     | $V_{DS} = 15V, I_D = 500\mu A$                                            |

| la co             | Drain to Source                   | LSK489A    | 2.5  | 5.5  | 8.5  | mA    | $V_{DG} = 15V, V_{GS} = 0$                                                |

| I <sub>DSS</sub>  | Saturation Current                | LSK489B    | 8.0  | 11.5 | 15.0 | ША    | $V_{\text{BG}} = 15V$ ; $V_{\text{GS}} = 0$                               |

| 1.                | Cata Operating Current            |            | -    | -2   | -25  | pА    | $V_{DG} = 15V, I_D = 200\mu A$                                            |

| lg                | Gate Operating Current            |            | -    | -0.8 | -10  | nA    | T <sub>A</sub> = 125°C                                                    |

| Igss              | Gate to Source Leakage            | Current    | -    | -    | -100 | pА    | $V_{DG} = -15V, V_{DS} = 0$                                               |

| Gfs               | Full Conductance Transconductance |            | 1500 | -    | -    | μS    | $V_{DG} = 15V, V_{GS} = 0, f = 1kHz$                                      |

| G <sub>fs</sub>   | Transconductance                  |            | 1000 | 1500 | -    | μS    | $V_{DG} = 15V, I_D = 500\mu A$                                            |

| Gos               | Full Output Conductance           |            | -    | -    | 40   | μS    | $V_{DG} = 15V, V_{GS} = 0$                                                |

| Gos               | Output Conductance                |            | -    | 1.8  | 2.7  | μS    | $V_{DG} = 15V, I_D = 200\mu A$                                            |

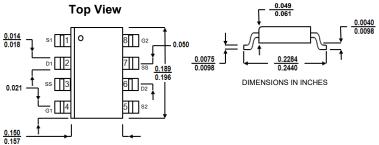

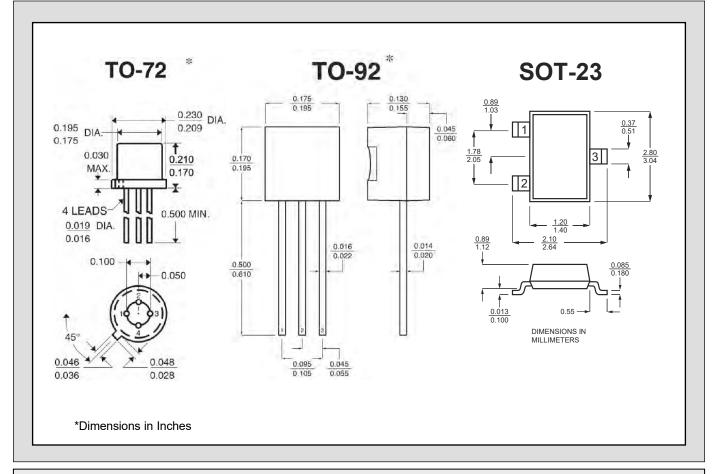

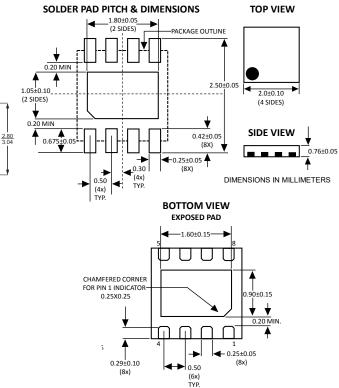

#### **Package Dimensions**

#### Notes

- 1. Absolute maximum ratings are limiting values above which serviceability may be impaired.

- 2. Pulse width  $\leq 2_{ms}$ .

- 3. All MIN/TYP/MAX Limits are absolute values. Negative signs indicate electrical polarity only.

- 4. Derate 2.4 mW/°C above 25°C.

- 5. Derate 4 mW/°C above 25°C.

Information furnished by Linear Integrated Systems is believed to be accurate and reliable. However, no responsibility is assumed for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Linear Integrated Systems.

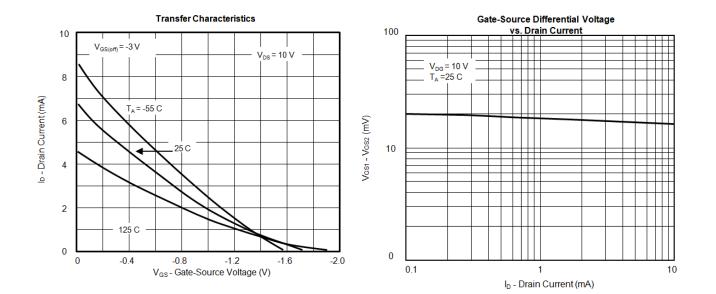

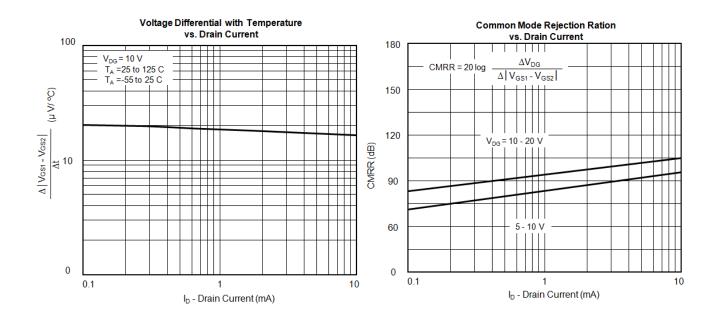

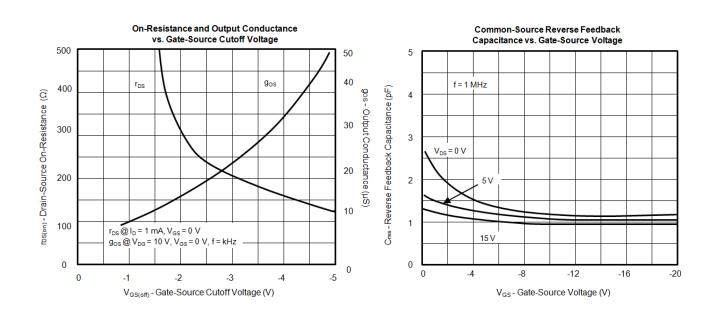

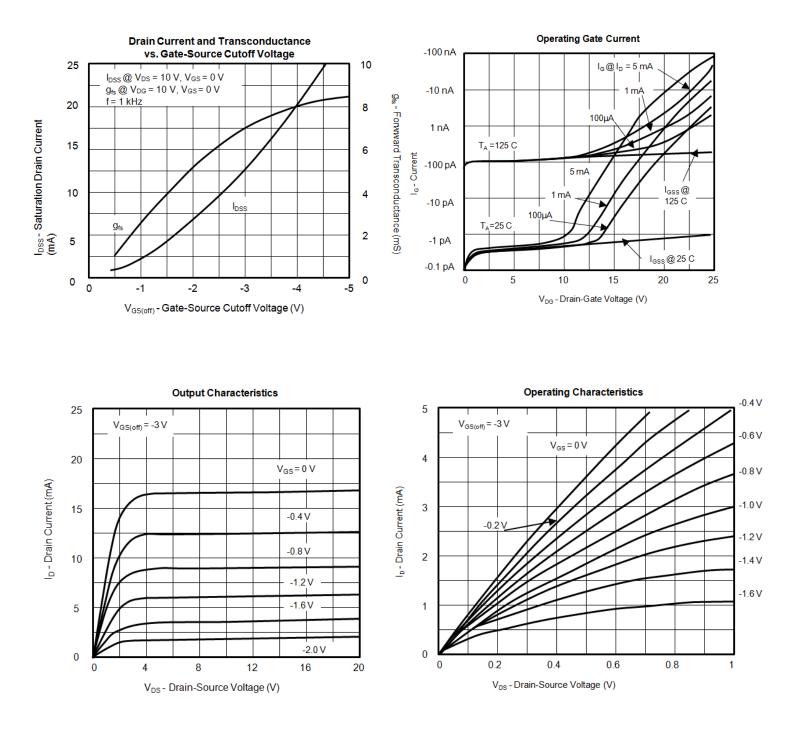

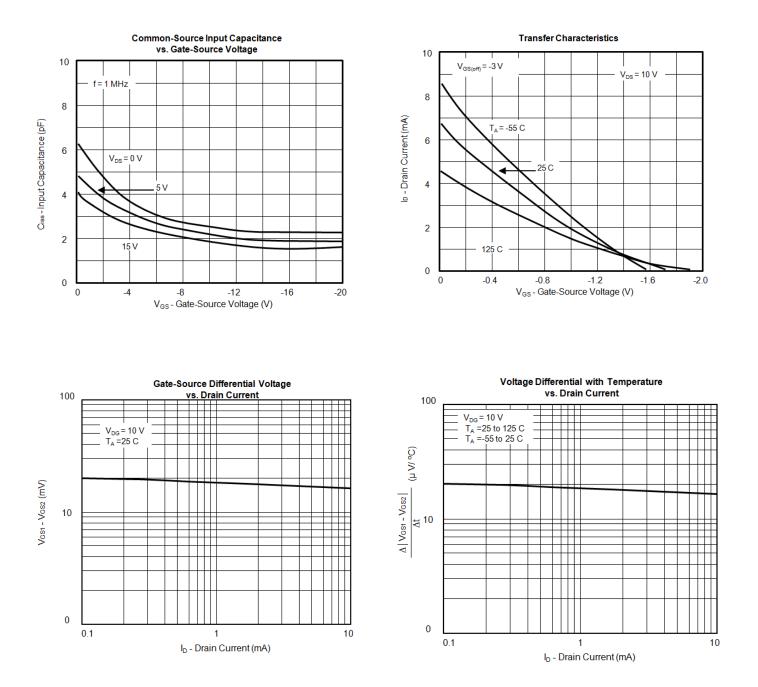

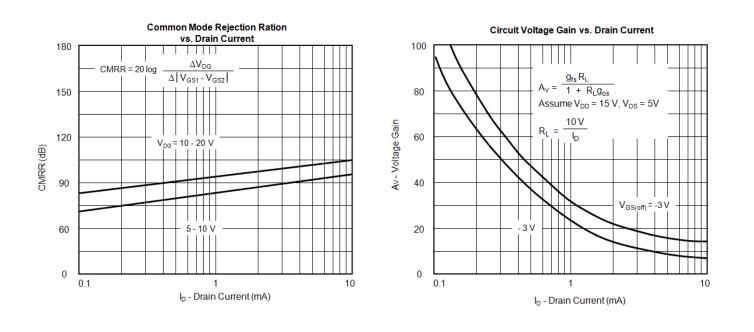

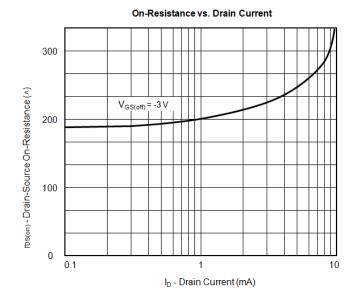

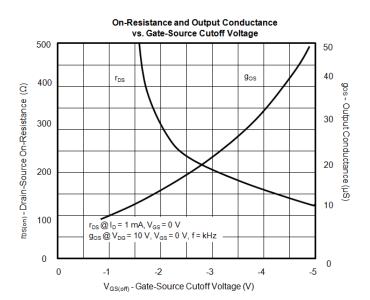

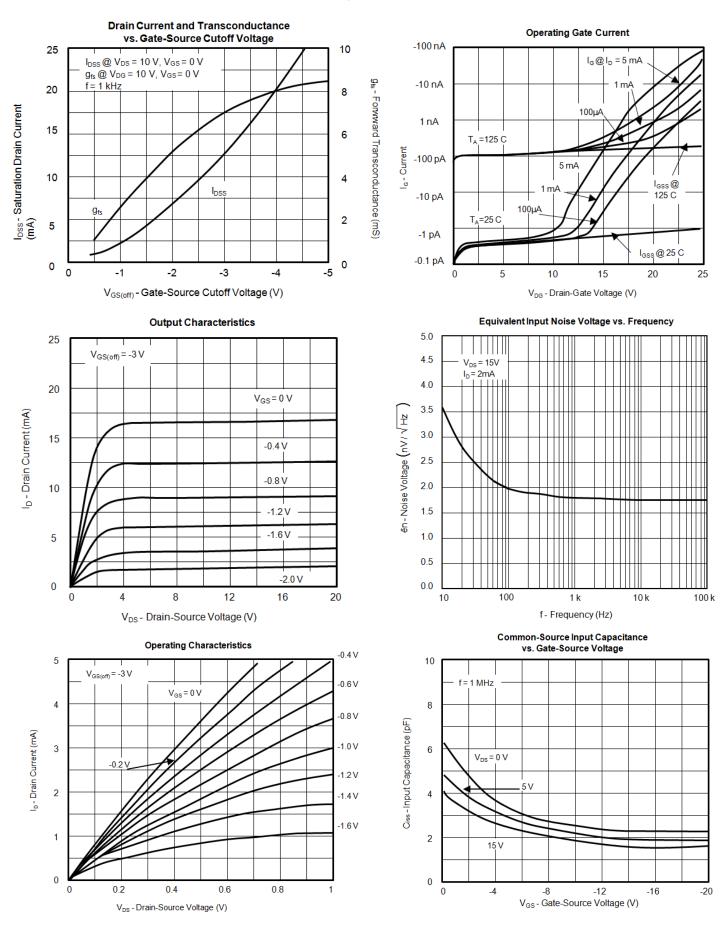

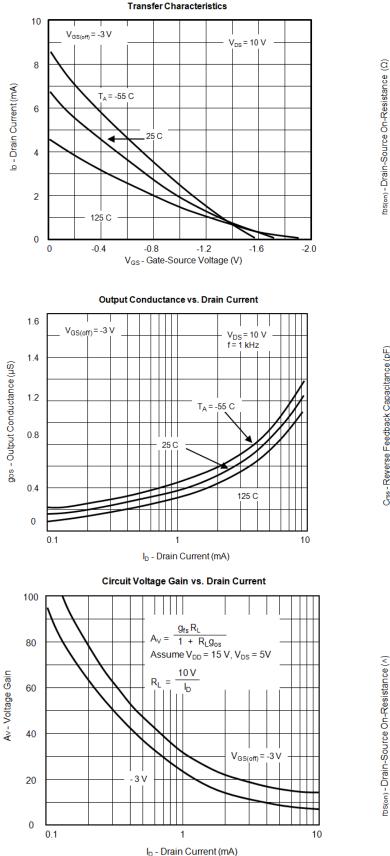

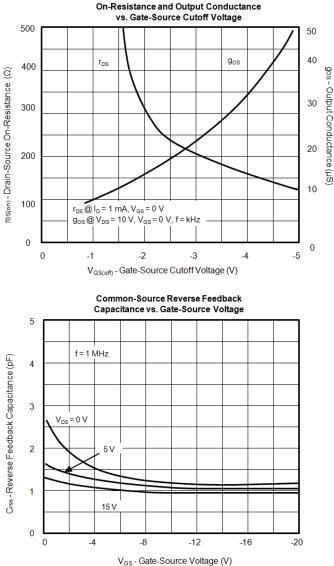

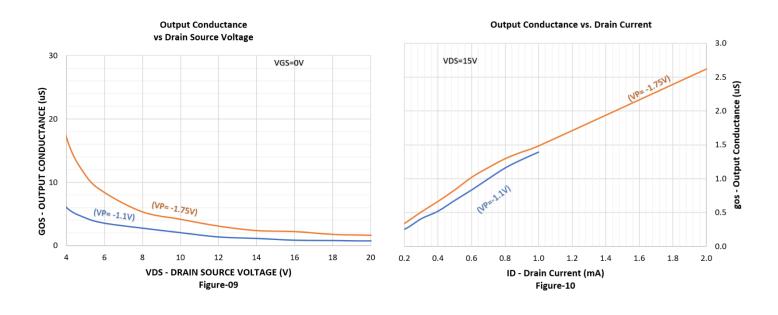

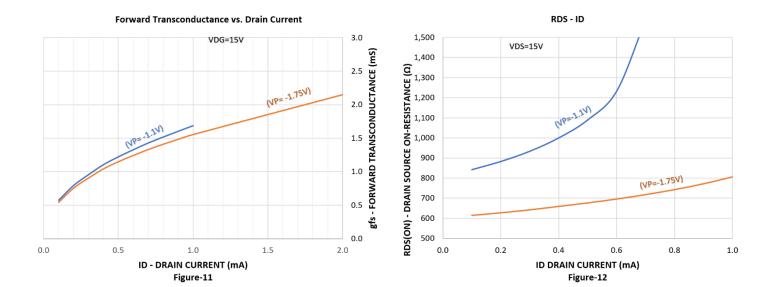

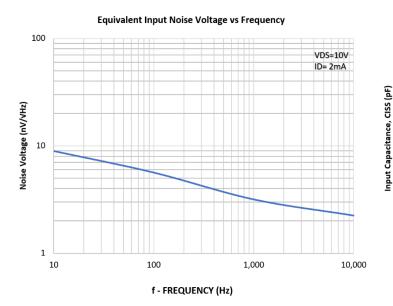

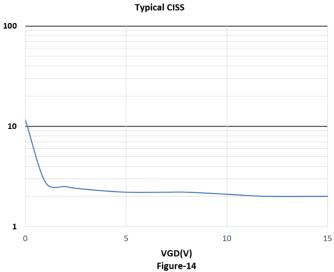

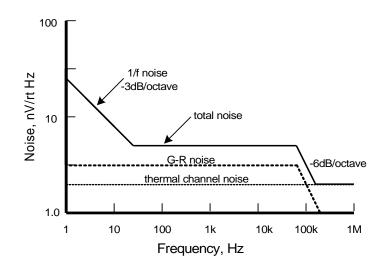

### **Typical Characteristics**

#### LSK489A/B

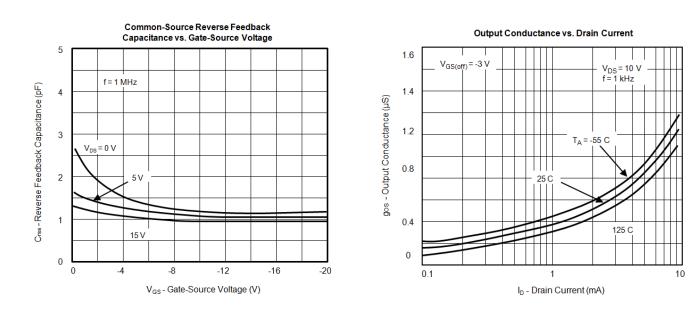

### **Typical Characteristics (Cont'd)**

www.linearsystems.com 2024 Data Book, Rev. no. A01

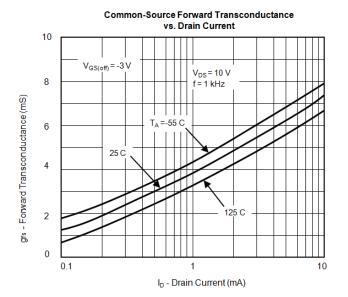

### **Typical Characteristics (Cont'd)**

### **Typical Characteristics (Cont'd)**

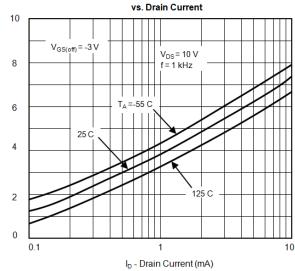

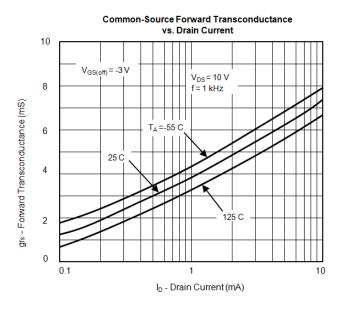

**Common-Source Forward Transconductance**

# LINEAR SYSTEMS

#### Over Three Decades of Quality Through Innovation

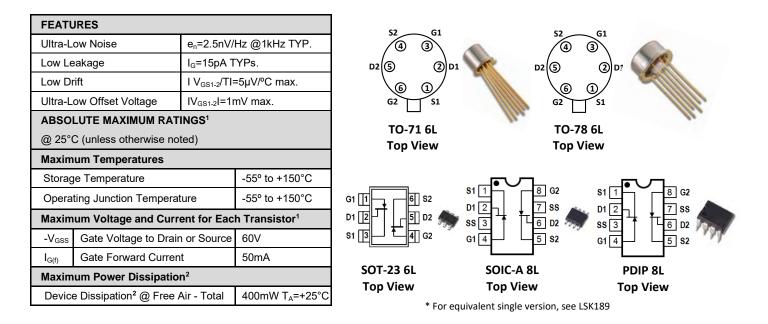

| FEATU             | FEATURES                                                                       |                      |                           |  |  |  |  |  |

|-------------------|--------------------------------------------------------------------------------|----------------------|---------------------------|--|--|--|--|--|

| LOW N             | OISE                                                                           | en=8nV/Hz TYP.       |                           |  |  |  |  |  |

| LOW L             | EAKAGE                                                                         | I <sub>G</sub> =10p  | DA TYP.                   |  |  |  |  |  |

| LOW D             | RIFT                                                                           | I V <sub>GS1-2</sub> | ₂/TI=5µV/⁰C max.          |  |  |  |  |  |

| LOW O             | FFSET VOLTAGE                                                                  | IV <sub>GS1-2</sub>  | I=2mV TYP.                |  |  |  |  |  |

| ABSOL             | UTE MAXIMUM RATING                                                             | S <sup>1</sup>       |                           |  |  |  |  |  |

| @ 25°C            | C (unless otherwise noted)                                                     |                      |                           |  |  |  |  |  |

| Maxim             | um Temperatures                                                                |                      |                           |  |  |  |  |  |

| Storag            | e Temperature                                                                  |                      | -55°C to +150°C           |  |  |  |  |  |

| Operat            | ing Junction Temperature                                                       |                      | -55°C to +150°C           |  |  |  |  |  |

| Maxim             | um Voltage and Current                                                         | for Eac              | h Transistor <sup>1</sup> |  |  |  |  |  |

| -V <sub>GSS</sub> | Gate Voltage to Drain or                                                       | Source               | 60V                       |  |  |  |  |  |

| I <sub>G(f)</sub> | Gate Forward Current                                                           |                      | 10mA                      |  |  |  |  |  |

| Maxim             | um Power Dissipation                                                           |                      |                           |  |  |  |  |  |

| Device            | Device Dissipation <sup>2</sup> @ Free Air - Total 400mW T <sub>A</sub> =+25°C |                      |                           |  |  |  |  |  |

# LS840 LS841 LS842

LOW NOISE LOW DRIFT LOW CAPACITANCE MONOLITHIC DUAL N-CHANNEL JFET AMPLIFIER

#### ELECTRICAL CHARACTERISTICS @ 25°C (unless otherwise noted)

| ELECTRICAL CHARACTERISTICS @ 25°C (unless otherwise noted) |                             |       |       |       |       |                                                                    |  |  |  |  |

|------------------------------------------------------------|-----------------------------|-------|-------|-------|-------|--------------------------------------------------------------------|--|--|--|--|

| SYMBOL                                                     | CHARACTERISTIC              | LS840 | LS841 | LS842 | UNITS | CONDITIONS                                                         |  |  |  |  |

| I V <sub>GS1-2</sub> / TI max.                             | Drift vs. Temperature       | 5     | 10    | 40    | µV/⁰C | $V_{DG} = 20V$ $I_D = 200\mu A$                                    |  |  |  |  |

|                                                            |                             |       |       |       |       | T <sub>A</sub> = -55°C to +125°C                                   |  |  |  |  |

| IV <sub>GS1-2</sub> I max.                                 | Offset Voltage              | 5     | 10    | 25    | mA    | V <sub>DG</sub> = 20V I <sub>D</sub> = 200µA                       |  |  |  |  |

| 0/400                                                      |                             |       | T)(D) |       |       | 001101710110                                                       |  |  |  |  |

| SYMBOL                                                     | CHARACTERISTIC <sup>3</sup> | MIN.  | TYP.  | MAX.  | UNITS | CONDITIONS                                                         |  |  |  |  |

| BV <sub>GSS</sub>                                          | Breakdown Voltage           | -60   |       |       | V     | $V_{DS}=0$ $I_{D}=-1nA$                                            |  |  |  |  |

| BVggo                                                      | Gate-to-Gate Breakdown      | ±60   |       |       | V     | $I_{GGO}=\pm 1\mu A$ $I_{D}=0$ $I_{S}=0$                           |  |  |  |  |

|                                                            | TRANSCONDUCTANCE            |       |       |       |       |                                                                    |  |  |  |  |

| G <sub>fss</sub>                                           | Full Conduction             | 1000  |       | 4000  | μS    | $V_{DG}$ = 20V $V_{GS}$ = 0 f = 1kHz                               |  |  |  |  |

| G <sub>fs</sub>                                            | Typical Conduction          | 500   |       | 1000  | μS    | V <sub>DG</sub> = 20V I <sub>D</sub> = 200µA                       |  |  |  |  |

| Gfs1<br>Gfs2                                               | Transconductance<br>Ratio   | 0.97  |       | 1.0   |       | V <sub>DG</sub> = 20V I <sub>D</sub> = 200µA; Note 4               |  |  |  |  |

|                                                            | DRAIN CURRENT               |       |       |       |       |                                                                    |  |  |  |  |

| IDSS                                                       | Full Conduction             | 0.5   | 2     | 5     | mA    | V <sub>DG</sub> = 20V V <sub>GS</sub> = 0                          |  |  |  |  |

| IDSS1<br>IDSS2                                             | Drain Current Ratio         | 0.95  |       | 1.0   |       |                                                                    |  |  |  |  |

|                                                            | GATE-SOURCE                 |       |       |       |       |                                                                    |  |  |  |  |

| V <sub>GS</sub> (off)                                      | Pinchoff Voltage            | -1    | -2    | -4.5  | V     | V <sub>DS</sub> = 20V I <sub>D</sub> = 1nA                         |  |  |  |  |

| V <sub>GS</sub>                                            | Operating Range             | -0.5  |       | -4    | V     | V <sub>DS</sub> = 20V I <sub>D</sub> = 200µA                       |  |  |  |  |

|                                                            | GATE CURRENT                |       |       |       |       |                                                                    |  |  |  |  |

| -lg                                                        | Operating                   |       | 10    | 50    | pА    | V <sub>DG</sub> = 20V I <sub>D</sub> =200µA                        |  |  |  |  |

| -l <sub>G</sub>                                            | High Temperature            |       |       | 50    | nA    | V <sub>DG</sub> = 20V I <sub>D</sub> =200µA T <sub>A</sub> =+125°C |  |  |  |  |

| -lg                                                        | Reduced VDG                 |       | 5     |       | pА    | V <sub>DG</sub> = 10V I <sub>D</sub> =200µA                        |  |  |  |  |

| -I <sub>GSS</sub>                                          | At Full Conduction          |       |       | 100   | pА    | V <sub>DG</sub> = 20V V <sub>DS</sub> =0                           |  |  |  |  |

| SYMBOL          | CHARACTERISTIC                                | MIN. | TYP. | MAX. | UNITS | CONDITIONS                  |                        |                       |

|-----------------|-----------------------------------------------|------|------|------|-------|-----------------------------|------------------------|-----------------------|

|                 | OUTPUT CONDUCTANCE                            |      |      |      |       |                             |                        |                       |

| Goss            | Full Conduction                               |      |      | 10   | μS    | V <sub>DG</sub> = 20V       | V <sub>GS</sub> = 0    |                       |

| G <sub>OS</sub> | Operating                                     |      | 0.1  | 1    | μS    | V <sub>DG</sub> = 20V       | I <sub>D</sub> = 200μΑ |                       |

| Gos 1-2         | Differential                                  |      | 0.01 | 0.1  | μS    |                             |                        |                       |

|                 | <b>COMMON MODE REJECTION</b>                  |      |      |      |       |                             |                        |                       |

| CMRR            | 20 log   V <sub>GS1-2</sub> / V <sub>DS</sub> |      | 100  |      | dB    | V <sub>DS</sub> = 10 to 20\ | /                      | I <sub>D</sub> =200µA |

| CMRR            | -20 109   V GS1-2/ V DS                       |      | 75   |      | dB    | V <sub>DS</sub> = 5 to 10V  |                        | I⊳=200µA              |

|                 | NOISE                                         |      |      |      |       |                             |                        |                       |

| NF              | Figure                                        |      |      | 0.5  | dB    | V <sub>DS</sub> = 20V       | V <sub>GS</sub> = 0    | R <sub>G</sub> =10M   |

|                 |                                               |      |      |      |       | f= 100Hz                    | NBW= 6Hz               |                       |

| en              | Voltage                                       |      |      | 10   | nV/Hz | V <sub>DS</sub> = 20V       | I⊳= 200µA              | f= 1KHz               |

|                 |                                               |      |      |      |       | NBW= 1Hz                    |                        |                       |

| en              | Voltage                                       |      |      | 15   | nV/Hz | V <sub>DS</sub> = 20V       | I <sub>D</sub> = 200μA | f= 10Hz               |

|                 |                                               |      |      |      |       | NBW= 1Hz                    |                        |                       |

|                 | CAPACITANCE                                   |      |      |      |       |                             |                        |                       |

| CISS            | Input                                         |      | 4    | 10   | pF    | V <sub>DS</sub> = 20V       | I <sub>D</sub> =200μΑ  |                       |

| Crss            | Reverse Transfer                              |      | 1.2  | 5    | pF    |                             |                        |                       |

| C <sub>DD</sub> | Drain-to-Drain                                |      | 0.1  |      | pF    | V <sub>DG</sub> = 20V       | I <sub>D</sub> = 200μΑ |                       |

#### NOTES:

- 1. These ratings are limiting values above which the serviceability of any semiconductor may be impaired

- 2. Derate 4mW/°C above 25°C

- 3. All MIN/TYP/MAX limits are absolute numbers. Negative signs indicate electrical polarity only.

- 4. Assumes smaller number in the numerator.

Information furnished by Linear Integrated Systems is believed to be accurate and reliable. However, no responsibility is assumed for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Linear Integrated Systems.

# LINEAR SYSTEMS

# **LS843 Series**

Over 30 Years of Quality Through Innovation

Low Noise, Monolithic Dual N-Channel JFET Amplifier

#### LOW INPUT CAPACITANCE MONOLITHIC DUAL N-CHANNEL JFET

#### Features

- Low Noise: e<sub>n</sub> = 2.5nV/√Hz (typ), f = 1kHz, NBW = 1Hz

- Very Low Common Source Input Capacitance of  $C_{\rm ISS}$  = 3pF typ and 8pF- max

- High Slew Rate

- Low Offset/Drift Voltage

- Low Gate Leakage  $\mathsf{I}_{\mathsf{GSS}}$  and  $\mathsf{I}_{\mathsf{G}}$

- High CMRR 102 dB

# Benefits

- Tight Differential Voltage Match vs. Current

- Improved Op Amp Speed Settling Time Accuracy

- Minimum Input Error Trimming Error Voltage

- Lower Intermodulation Distortion

#### Applications

- Wideband Differential Amplifiers

- High Speed Temperature Compensated Single Ended Input Amplifier Amps

- High Speed Comparators

- Impedance Converters

- Sonobouys and Hydrophones

- Acoustic Sensors

#### Description

The LS843 Series is the industry's lowest input capacitance and low-noise monolithic dual N-Channel JFET. Low input capacitance substantially reduces intermodulation distortion. In addition, these dual JFETs feature tight offset voltage and low drift over temperature range, and are targeted for use in a wide range of precision instrumentation and sensor applications.

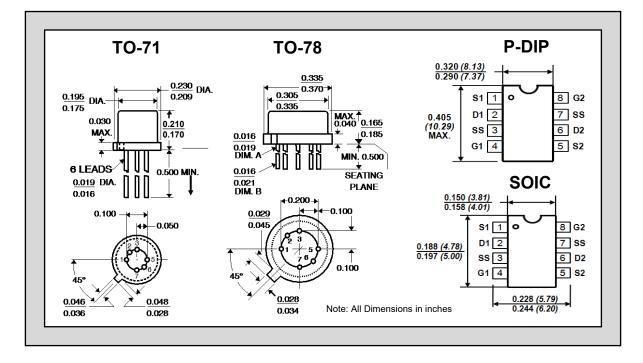

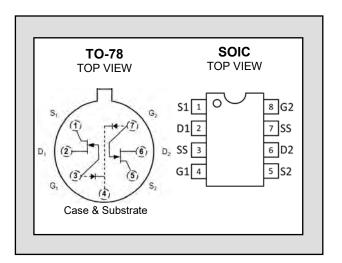

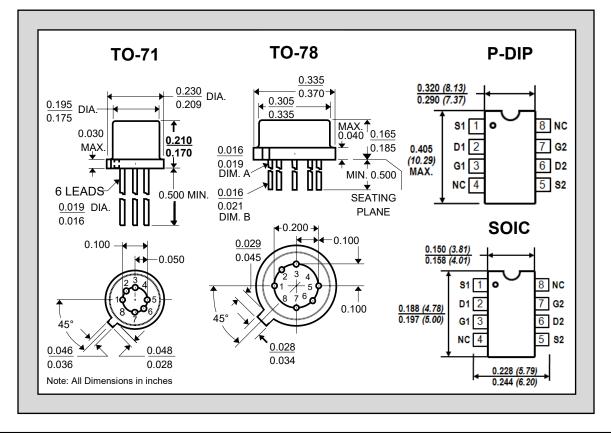

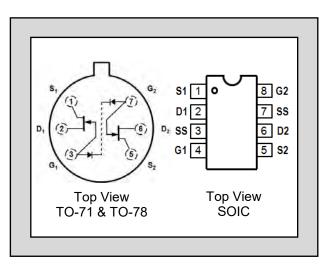

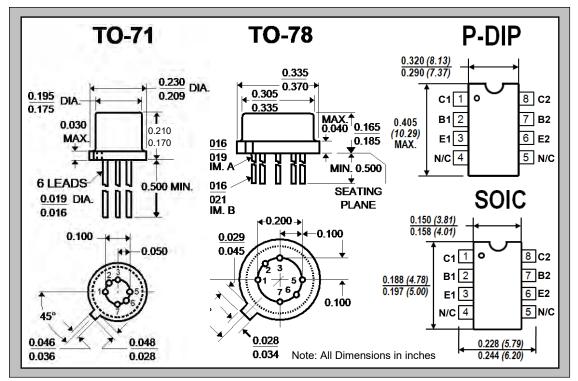

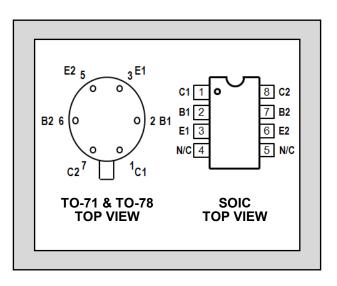

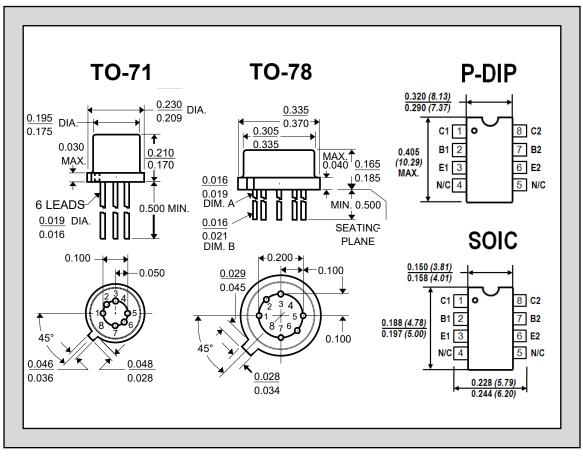

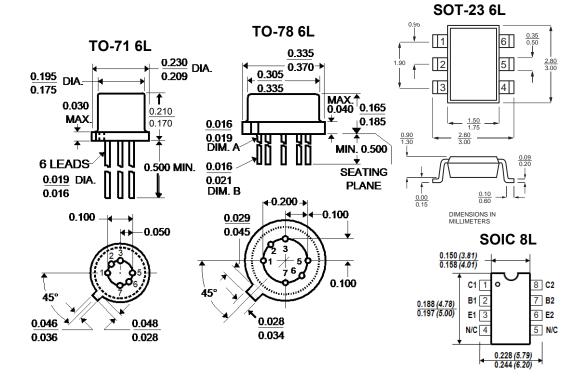

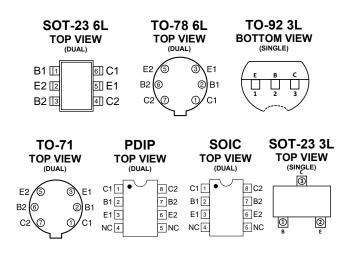

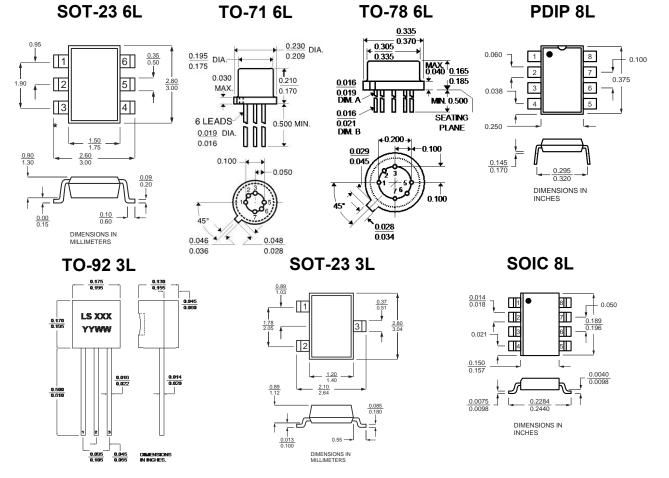

The LS843 Series is available in surface mount plastic SOIC 8L, PDIP 8L and SOT-23 6L packages. Additionally, it is offered in thru-hole metal cans; the TO-71 6L and TO-78 6L package.

For an equivalent single N-Channel version refer to the LSK189 datasheet. LS843 Series TO-71 6L and SOIC 8L are fit, form and pin compatible to the same LSK389 product.

The LS843 Series provides an increase in capabilities for a wide range of low-noise applications.

The most significant aspect of the LS843 Series is how it combines a noise level comparable with the LSK389 while having much lower gate-to-drain capacitance, 4pF versus the 25pF. The slightly higher noise of the LS843 Series, versus the LSK389, is not significant in most instances, while the much lower capacitance enables designers to produce simpler, more elegant circuit designs with fewer devices that cost less in production.

Like the Linear Systems LSK389, the LS843 Series features a unique design construction of interleaving both JFETs on the same piece of silicon to provide excellent matching and thermal tracking, as well a low-noise profile having nearly zero popcorn noise.

### Electrical Characteristics @ 25°C (unless otherwise noted)

| SYMBOL                         | CHARACTERISTIC        | LS843 | LS844 | LS845 | UNITS | CONDITIONS                       |                        |

|--------------------------------|-----------------------|-------|-------|-------|-------|----------------------------------|------------------------|

| I V <sub>GS1-2</sub> / TI max. | Drift vs. Temperature | 5     | 10    | 25    | µV/⁰C | V <sub>DG</sub> = 10V            | I <sub>D</sub> = 500μA |

| 1 V 031-27 TT Max.             |                       | Ũ     | 10    | 20    |       | T <sub>A</sub> = -55°C to +125°C |                        |

| IV <sub>GS1-2</sub> I max.     | Offset Voltage        | 1     | 5     | 15    | mV    | V <sub>GS</sub> = 10V            | I⊳= 500µA              |

| SYMBOL                                | CHARACTERISTIC                        | MIN. | TYP. | MAX. | UNITS | CONDITIONS              |                        |                        |

|---------------------------------------|---------------------------------------|------|------|------|-------|-------------------------|------------------------|------------------------|

| BV <sub>GSS</sub>                     | Breakdown Voltage                     | -60  |      |      | V     | V <sub>DS</sub> = 0     | I⊳= -1nA               |                        |

| BV <sub>GGO</sub>                     | Gate-to-Gate Breakdown                | ±60  |      |      | V     | I <sub>GGO</sub> = ±1μΑ | I <sub>D</sub> = 0     | I <sub>S</sub> = 0     |

| G <sub>fss</sub>                      | TRANSCONDUCTANCE<br>Full Conduction   | 1500 |      |      | μS    | V <sub>DS</sub> = 15V   | V <sub>GS</sub> = 0    | f = 1kHz               |

| G <sub>fs</sub>                       | Typical Conduction                    | 1000 | 1500 |      | μS    | V <sub>DS</sub> = 15V   | 1 - 5004               |                        |

| Gfs1-2/Gfs1                           | Mismatch                              |      | 0.6  | 3    | %     | VDS= 15V                | I <sub>D</sub> = 500µA |                        |

| IDSS                                  | DRAIN CURRENT<br>Full Conduction      | 1.5  | 5    | 15   | mA    | Vos= 15V                | V <sub>GS</sub> = 0    |                        |

| I <sub>DSS1-2</sub> /I <sub>DSS</sub> | Mismatch at Full Conduction           |      | 1    | 5    | %     | VDS- 13V                | VGS- U                 |                        |

| V <sub>GS</sub> (off)                 | GATE VOLTAGE<br>Pinchoff Voltage      | -1   |      | -3.5 | v     | V <sub>DS</sub> = 15V   | I₀= 1nA                |                        |

| V <sub>GS</sub>                       | Operating Range                       | -0.5 |      | -3.5 | V     | V <sub>DS</sub> = 15V   | I <sub>D</sub> = 500μA |                        |

| -lg                                   | GATE CURRENT<br>Operating             |      | 15   | 50   | pА    | V <sub>DG</sub> = 15V   | I <sub>D</sub> = 500μΑ |                        |

| -lg                                   | High Temperature                      |      |      | 50   | nA    | V <sub>DG</sub> = 15V   | I⊳= 500µA              | T <sub>A</sub> =+125°C |

| -lg                                   | Reduced VDG                           |      | 5    | 30   | pА    | V <sub>DG</sub> = 3V    | I⊳= 500µA              |                        |

| -lgss                                 | At Full Conduction                    |      |      | 100  | pА    | V <sub>GS</sub> = 15V   | V <sub>GS</sub> = 0    |                        |

| Goss                                  | OUTPUT CONDUCTANCE<br>Full Conduction |      |      | 40   | μS    | V <sub>DS</sub> = 15V   | V <sub>GS</sub> = 0    |                        |

| Gos                                   | Operating                             |      | 2.0  | 2.7  | μS    | V <sub>DS</sub> = 15V   | In- 2000               |                        |

| Gos 1-2                               | Differential                          |      | 0.02 | 0.2  | μS    | vDs- 15v                | I <sub>D</sub> = 200µA |                        |

| SYMBOL           | CHARACTERISTIC                                 | MIN. | TYP. | MAX. | UNITS | CONDITIONS                                                     |                       |

|------------------|------------------------------------------------|------|------|------|-------|----------------------------------------------------------------|-----------------------|

|                  | COMMON MODE REJECTION                          |      |      |      |       |                                                                |                       |

| CMRR             | -20 log ΔV <sub>GS1-2</sub> / ΔV <sub>DS</sub> | 90   | 100  |      | dB    | V <sub>DS</sub> = 10 to 20V                                    | I⊳= 500µA             |

| CMRR             |                                                |      | 85   |      | dB    | V <sub>DS</sub> = 5 to 10V                                     | I⊳= 500µA             |

| NF               | <u>NOISE</u><br>Figure                         | -    |      | 0.5  | dB    | V <sub>DS</sub> = 15V V <sub>GS</sub> = 0<br>f= 100Hz NBW= 6Hz | R <sub>G</sub> = 10MΩ |

| en               | Voltage                                        |      |      | 7    | nV/Hz | V <sub>DS</sub> = 15V I <sub>D</sub> = 500µA<br>NBW= 1Hz       | f= 1kHz               |

| en               | Voltage                                        |      |      | 11   | nV/Hz | V <sub>DS</sub> = 15V I <sub>D</sub> = 500µA<br>NBW= 1Hz       | f= 10Hz               |

| C <sub>ISS</sub> | CAPACITANCE<br>Input                           |      |      | 8    | pF    | V <sub>DS</sub> = 15V I <sub>D</sub> = 500µA                   | f= 1mHz               |

| Crss             | Reverse Transfer                               |      |      | 3    | pF    |                                                                |                       |

| C <sub>DD</sub>  | Drain-to-Drain                                 |      | 0.5  |      | pF    | V <sub>DD</sub> = 15V I <sub>D</sub> = 500µA                   | f= 1mHz               |

#### Notes:

- 1. Absolute maximum ratings are limiting values above which serviceability may be impaired.

- 2. Pulse width  $\leq 2_{ms}$ .

- 3. All MIN/TYP/MAX Limits are absolute values. Negative signs indicate electrical polarity only.

- 4. Derate 2.4 mW/°C above 25°C.

5. Derate 4 mW/°C above 25°C.

Information furnished by Linear Integrated Systems is believed to be accurate and reliable. However, no responsibility is assumed for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Linear Integrated Systems.

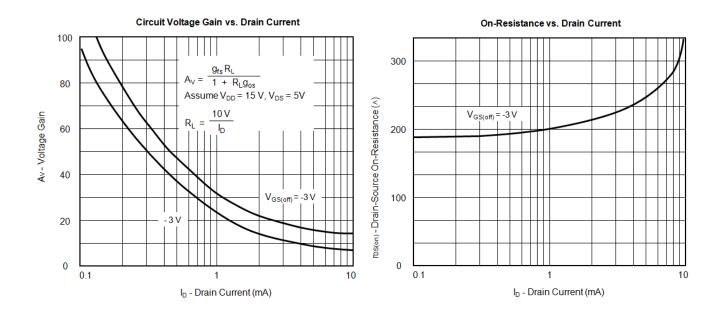

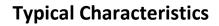

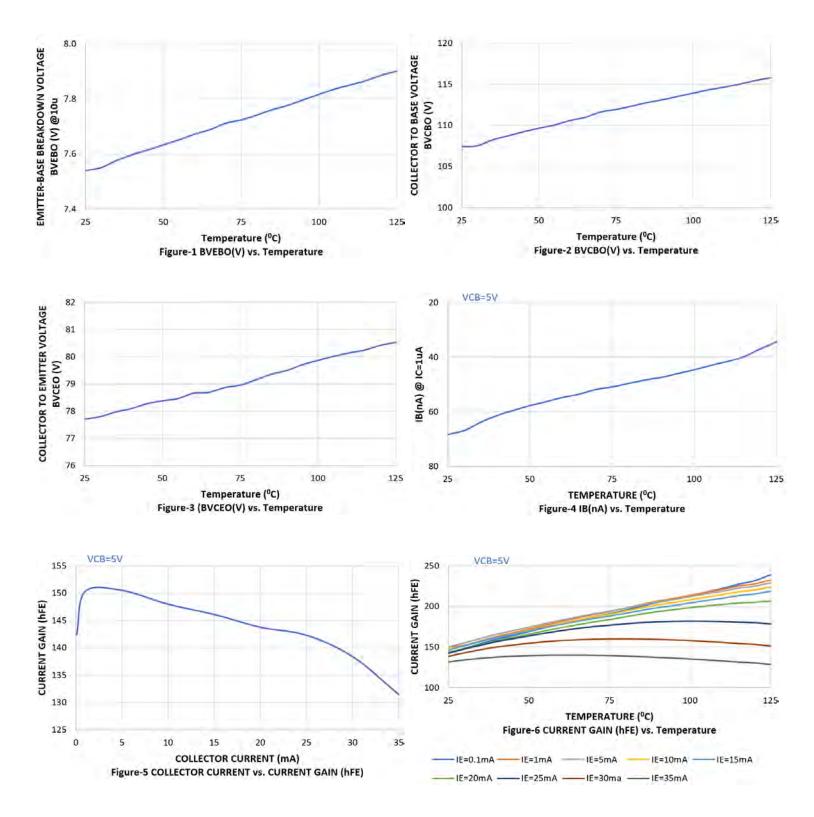

### **Typical Characteristics**

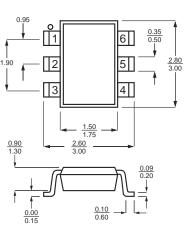

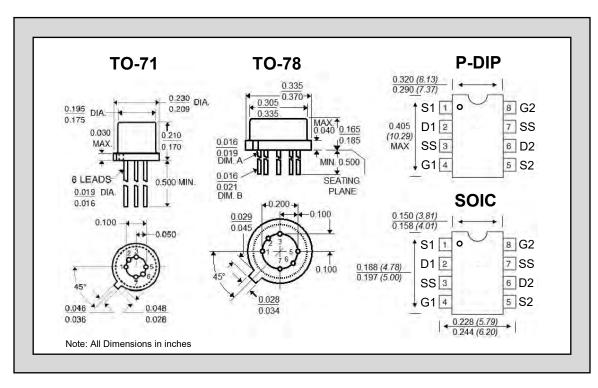

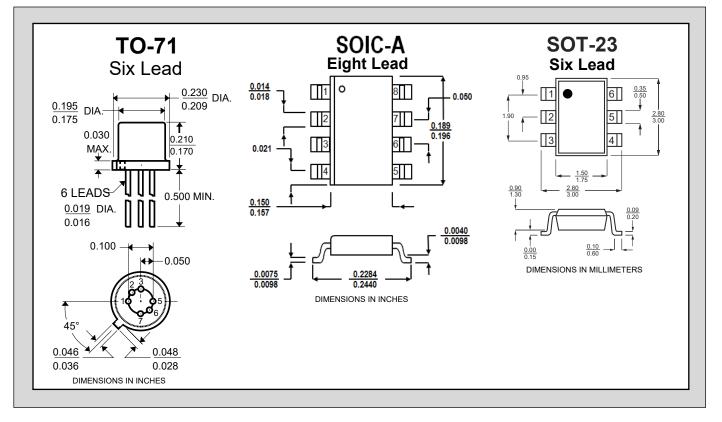

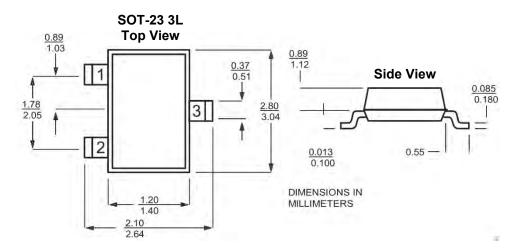

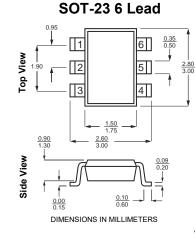

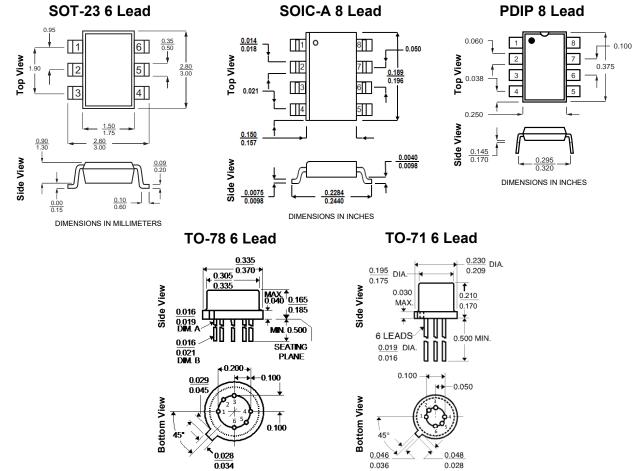

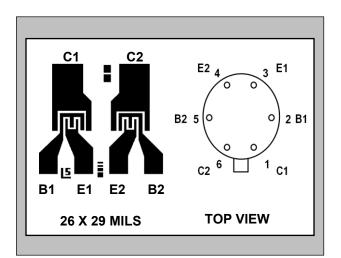

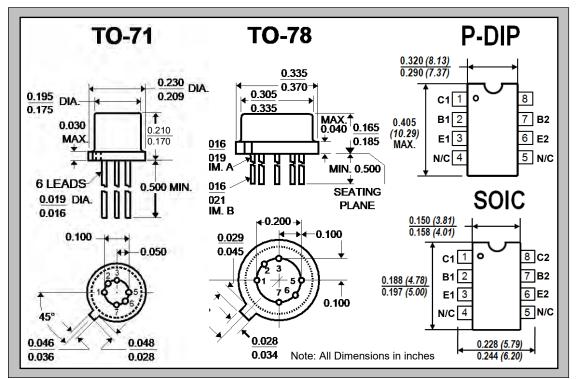

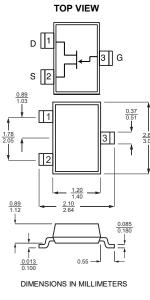

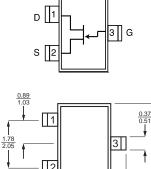

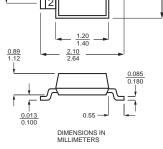

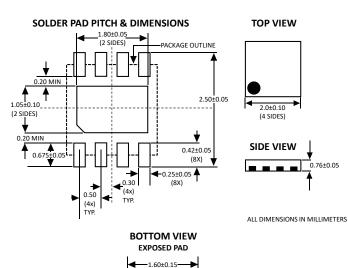

#### Package Dimensions:

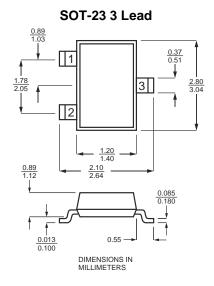

**SOT-23**

6 Lead

#### **Ordering Information:**

| Standard Part Call-Out            |                                       |                              |  |  |  |  |  |  |  |  |  |

|-----------------------------------|---------------------------------------|------------------------------|--|--|--|--|--|--|--|--|--|

| LS843 TO-71 6L RoHS               | LS844 TO-71 6L RoHS                   | LS845 TO-71 6L RoHS          |  |  |  |  |  |  |  |  |  |

| LS843 TO-78 6L RoHS               | LS844 TO-78 6L RoHS                   | LS845 TO-78 6L RoHS          |  |  |  |  |  |  |  |  |  |

| LS843 SOT-23 6L RoHS              | LS844 SOT-23 6L RoHS                  | LS845 SOT-23 6L RoHS         |  |  |  |  |  |  |  |  |  |

| LS843 SOIC 8L RoHS                | LS844 SOIC 8L RoHS                    | LS845 SOIC 8L RoHS           |  |  |  |  |  |  |  |  |  |

| LS843 PDIP 8L RoHS                | LS844 PDIP 8L RoHS                    | LS845 PDIP 8L RoHS           |  |  |  |  |  |  |  |  |  |

| Custom Part Call-Out (Custom Part | s Include SEL + 4 Digit Numeric Code) |                              |  |  |  |  |  |  |  |  |  |

| LS843 TO-71 6L RoHS SELXXXX       | LS844 TO-71 6L RoHS SELXXXX           | LS845 TO-71 6L RoHS SELXXXX  |  |  |  |  |  |  |  |  |  |

| LS843 TO-78 6L RoHS SELXXXX       | LS844 TO-78 6L RoHS SELXXXX           | LS845 TO-78 6L RoHS SELXXXX  |  |  |  |  |  |  |  |  |  |

| LS843 SOT-23 6L RoHS SELXXXX      | LS844 SOT-23 6L RoHS SELXXXX          | LS845 SOT-23 6L RoHS SELXXXX |  |  |  |  |  |  |  |  |  |

| LS843 SOIC 8L RoHS SELXXXX        | LS844 SOIC 8L RoHS SELXXXX            | LS845 SOIC 8L RoHS SELXXXX   |  |  |  |  |  |  |  |  |  |

| LS843 PDIP 8L RoHS SELXXXX        | LS844 PDIP 8L RoHS SELXXXX            | LS845 PDIP 8L RoHS SELXXXX   |  |  |  |  |  |  |  |  |  |

# LINEAR SYSTEMS

#### Over 30 Years of Quality Through Innovation

| FEATURES                                                                   |                              |  |  |  |  |  |  |

|----------------------------------------------------------------------------|------------------------------|--|--|--|--|--|--|

| Improved Replacement for SILICONIX, FAIRCHILD, & NATIONAL: 2N5911 & 2N5912 |                              |  |  |  |  |  |  |

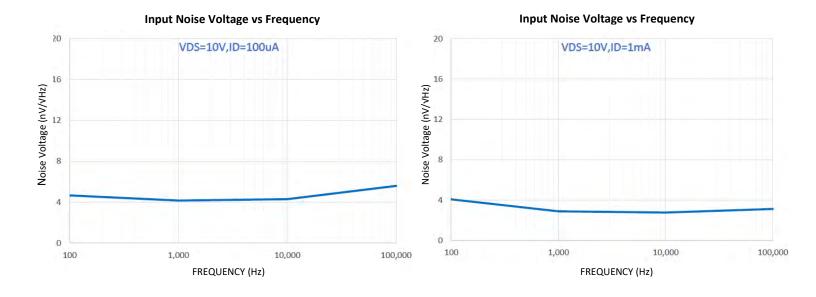

| LOW NOISE (10kHz)                                                          | $e_n \sim 4 n V / \sqrt{Hz}$ |  |  |  |  |  |  |

| HIGH TRANSCONDUCTANCE (100MHz)                                             | g <sub>fs</sub> ≥ 4000µS     |  |  |  |  |  |  |

| ABSOLUTE MAXIMUM RATINGS <sup>1</sup>                                      |                              |  |  |  |  |  |  |

| @ 25 °C (unless otherwise stated)                                          |                              |  |  |  |  |  |  |

| Maximum Temperatures                                                       |                              |  |  |  |  |  |  |

| Storage Temperature                                                        | -55 to +150 °C               |  |  |  |  |  |  |

| Operating Junction Temperature                                             | -55 to +150 °C               |  |  |  |  |  |  |

| Maximum Power Dissipation                                                  |                              |  |  |  |  |  |  |

| Continuous Power Dissipation (Total) <sup>4</sup>                          | 500mW                        |  |  |  |  |  |  |

| Maximum Currents                                                           |                              |  |  |  |  |  |  |

| Gate Current                                                               | 50mA                         |  |  |  |  |  |  |

| Maximum Voltages                                                           |                              |  |  |  |  |  |  |

| Gate to Drain                                                              | -25V                         |  |  |  |  |  |  |

| Gate to Source                                                             | -25V                         |  |  |  |  |  |  |

# LS5911 LS5912 LS5912C

#### IMPROVED LOW NOISE WIDEBAND MONOLITHIC DUAL N-CHANNEL JFET AMPLIFIER

#### MATCHING ELECTRICAL CHARACTERISTICS @25 °C (unless otherwise stated)

| CVMDOI                                                      |                                                                   | TVD | LS5  | 911 | LS5  | 912 | LS5912C |     |       | CONDITIONS                                                                    |

|-------------------------------------------------------------|-------------------------------------------------------------------|-----|------|-----|------|-----|---------|-----|-------|-------------------------------------------------------------------------------|

| SYMBOL                                                      | CHARACTERISTIC                                                    | TYP | MIN  | MAX | MIN  | MAX | MIN     | MAX | UNIT  | CONDITIONS                                                                    |

| VGS1-VGS2                                                   | Differential Gate to Source<br>Cutoff Voltage                     |     |      | 10  |      | 15  |         | 40  | mV    | V <sub>DG</sub> = 10V, I <sub>D</sub> = 5mA                                   |

| $\frac{\Delta  V_{\text{GS1}} - V_{\text{GS2}} }{\Delta T}$ | Differential Gate to Source<br>Voltage Change with<br>Temperature |     |      | 20  |      | 40  |         | 40  | µV/°C | V <sub>DG</sub> = 10V, I <sub>D</sub> = 5mA<br>T <sub>A</sub> = -55 to +125°C |

| DSS1<br>DSS2                                                | Saturation Drain Current<br>Ratio                                 |     | 0.95 | 1   | 0.95 | 1   | 0.95    | 1   |       | V <sub>DS</sub> = 10V, V <sub>GS</sub> = 0V<br>Notes 2, 3                     |

| G1- G2                                                      | Differential Gate Current                                         |     |      | 20  |      | 20  |         | 20  | nA    | V <sub>DG</sub> = 10V, I <sub>D</sub> = 5mA<br>T <sub>A</sub> = +125°C        |

| $\frac{g_{fs1}}{g_{fs2}}$                                   | Forward Transconductance<br>Ratio                                 |     | 0.95 | 1   | 0.95 | 1   | 0.95    | 1   |       | $V_{DS} = 10V, I_D = 5mA$<br>f = 1kHz <sup>3</sup>                            |

| CMRR                                                        | Common Mode Rejection<br>Ratio                                    | 85  |      |     |      |     |         |     | dB    | $V_{DG} = 5V$ to 10V<br>$I_D = 5mA$                                           |

#### STATIC ELECTRICAL CHARACTERISTICS @25 °C (unless otherwise stated)

| SYM.                 | CHARACTERISTIC                 | ТҮР | LSS  | 5911 | LS5  | 912 | LS59 | 912C | UNIT       | CONDITIONS                           |  |

|----------------------|--------------------------------|-----|------|------|------|-----|------|------|------------|--------------------------------------|--|

| 5111.                | CHARACTERISTIC                 | ITP | MIN  | MAX  | MIN  | MAX | MIN  | MAX  | UNIT       | CONDITIONS                           |  |

| BV <sub>GSS</sub>    | Gate to Source Breakdown       |     | -25  |      | -25  |     | -25  |      |            | $I_{G}$ = -1µA, $V_{DS}$ = 0V        |  |

| V <sub>GS(off)</sub> | Gate to Source Cutoff Voltage  |     | -1   | -5   | -1   | -5  | -1   | -5   | V          | $V_{DS}$ = 10V, $I_{D}$ = 1nA        |  |

| V <sub>GS(F)</sub>   | Gate to Source Forward Voltage | 0.7 |      |      |      |     |      |      | v          | $I_G$ = 1mA, $V_{DS}$ = 0V           |  |

| V <sub>GS</sub>      | Gate to Source Voltage         |     | -0.3 | -4   | -0.3 | -4  | -0.3 | -4   |            | $V_{DG}$ = 10V, $I_{G}$ = 5mA        |  |

| I <sub>DSS</sub>     | Drain to Source Saturation     |     | 7    | 40   | 7    | 40  | 7    | 40   | mA         | $V_{DS}$ = 10V, $V_{GS}$ = 0V        |  |

| Igss                 | Gate Leakage Current           | -1  |      | -50  |      | -50 |      | -50  | <b>n</b> A | $V_{GS}$ = -15V, $V_{DS}$ = 0V       |  |

| lg                   | Gate Operating Current         | -1  |      | -50  |      | -50 |      | -50  | pА         | $V_{DG}$ = 10V, $I_{D}$ = 5mA        |  |

| IG1G2                | Gate to Gate Isolation Current |     |      | ±1   |      | ±1  |      | ±1   | uA         | $V_{G1}-V_{G2}=\pm 25V_{ID}=I_{S}=0$ |  |

| OVM         | CHARACTERISTIC       |                   | TVD  | LS5  | 911   | LS5  | 912   | LS5  | 912C  |        | CONDITIONS                                                                       |  |

|-------------|----------------------|-------------------|------|------|-------|------|-------|------|-------|--------|----------------------------------------------------------------------------------|--|

| SYM.        | CHARACTERISTIC       |                   | ТҮР  | MIN  | MAX   | MIN  | MAX   | MIN  | MAX   | UNIT   | CONDITIONS                                                                       |  |

| <i>a.</i>   | Forward              | f = 1 kHz         |      | 4000 | 10000 | 4000 | 10000 | 4000 | 10000 |        |                                                                                  |  |

| <b>g</b> fs | Transconductance     | <i>f</i> = 100MHz | 7000 |      |       |      |       |      |       | μS     | $V_{20} = 10 V_{10} = 5 m A$                                                     |  |

| ~           | Output Conductores   | f = 1 kHz         |      |      | 100   |      | 100   |      | 100   | μο     | $V_{DG} = 10V, I_{D} = 5mA$                                                      |  |

| gos         | Output Conductance   | f = 100MHz        | 120  |      |       |      |       |      |       |        |                                                                                  |  |

| Ciss        | Input Capacitance    |                   |      |      | 5     |      | 5     |      | 5     | ~F     | V <sub>DG</sub> = 10V, I <sub>D</sub> = 5mA                                      |  |

| Crss        | Reverse Transfer Cap | pacitance         |      |      | 1.2   |      | 1.2   |      | 1.2   | pF     | f = 1MHz                                                                         |  |

| NF          | Noise Figure         |                   |      |      | 1     |      | 1     |      | 1     | dB     | V <sub>DG</sub> = 10V, I <sub>D</sub> = 5mA<br>f = 10kHz, R <sub>G</sub> = 100KΩ |  |

|             | Equivalent Input     | <i>f</i> = 100Hz  | 7    |      | 20    |      | 20    |      | 20    | nV/√Hz | $V_{DG} = 10V, I_D = 5mA$<br>f = 100Hz                                           |  |

| en          | Noise Voltage        | <i>f</i> = 10kHz  | 4    |      | 10    |      | 10    |      | 10    | nV/√Hz | $V_{DG} = 10V, I_D = 5mA$<br>f = 10kHz                                           |  |

#### NOTES:

- 1. Absolute maximum ratings are limiting values above which serviceability may be impaired.

- 2. Pulse Test: PW ≤ 300µs Duty Cycle ≤ 3%

- 3. Assumes smaller value in numerator.

- 4. Derate 4mW/°C above 25°C.

Information furnished by Linear Integrated Systems is believed to be accurate and reliable. However, no responsibility is assumed for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Linear Integrated Systems.

# LINEAR SYSTEMS

# Improved Standard Products<sup>®</sup>

| FEATURES                                             |                        |  |  |  |  |  |  |  |

|------------------------------------------------------|------------------------|--|--|--|--|--|--|--|

| Direct Replacement for SILICONIX U/SST440 & U/SST441 |                        |  |  |  |  |  |  |  |

| HIGH CMRR                                            | CMRR ≥ 85dB            |  |  |  |  |  |  |  |

| LOW GATE LEAKAGE                                     | l <sub>GSS</sub> ≤ 1pA |  |  |  |  |  |  |  |

| ABSOLUTE MAXIMUM RATINGS <sup>1</sup>                |                        |  |  |  |  |  |  |  |

| @ 25 °C (unless otherwise stated)                    |                        |  |  |  |  |  |  |  |

| Maximum Temperatures                                 |                        |  |  |  |  |  |  |  |

| Storage Temperature                                  | -55 to +150 °C         |  |  |  |  |  |  |  |

| Operating Junction Temperature                       | -55 to +150 °C         |  |  |  |  |  |  |  |

| Maximum Power Dissipation @ TA = 25°C                |                        |  |  |  |  |  |  |  |

| Continuous Power Dissipation (Total)                 | 500mW                  |  |  |  |  |  |  |  |

| Maximum Currents                                     |                        |  |  |  |  |  |  |  |

| Gate Current                                         | 50mA                   |  |  |  |  |  |  |  |

| Maximum Voltages                                     |                        |  |  |  |  |  |  |  |

| Gate to Drain                                        | -25V                   |  |  |  |  |  |  |  |

| Gate to Source                                       | -25V                   |  |  |  |  |  |  |  |

| Gate to Gate                                         | ±50V                   |  |  |  |  |  |  |  |

# <u>U/SST440, 441</u>

#### WIDEBAND HIGH GAIN MONOLITHIC DUAL N-CHANNEL JFET AMPLIFIER

#### MATCHING CHARACTERISTICS @ 25 °C (unless otherwise stated)

| SYMBOL                                                                   | CHARACTERISTIC                                                        |          |  | TYP  | MAX | UNITS | CONDITIONS                                                                    |

|--------------------------------------------------------------------------|-----------------------------------------------------------------------|----------|--|------|-----|-------|-------------------------------------------------------------------------------|

| VGS1 - VGS2                                                              | Differential Gate to                                                  | U/SST440 |  |      | 10  | mV    | V <sub>DG</sub> = 10V, I <sub>D</sub> = 5mA                                   |

|                                                                          | Source Cutoff Voltage                                                 | U/SST441 |  |      | 20  | mv    | VDG = 10V, ID = 5IIIA                                                         |

| $\frac{\Delta \left  V_{\text{GS1}} - V_{\text{GS2}} \right }{\Delta T}$ | Differential Gate to Source Cutoff<br>Voltage Change with Temperature |          |  | 20   |     | µV/°C | V <sub>DG</sub> = 10V, I <sub>D</sub> = 5mA<br>T <sub>A</sub> = -55 to +125°C |

| IDSS1<br>IDSS2                                                           | Gate to Source Saturation Current Ratio <sup>3</sup>                  |          |  | 0.98 |     |       | V <sub>DS</sub> = 10V, V <sub>GS</sub> = 0V                                   |

| $\frac{g_{fs1}}{g_{fs2}}$                                                | Forward Transconductance Ratio <sup>2</sup>                           |          |  | 0.97 |     |       | V <sub>DS</sub> = 10V, I <sub>D</sub> = 5mA, <i>f</i> = 1kHz                  |

| CMRR                                                                     | Common Mode Rejection Ra                                              | itio     |  | 85   |     | dB    | $V_{DG}$ = 5 to 10V, $I_D$ = 5mA                                              |

#### ELECTRICAL CHARACTERISTICS @ 25 °C (unless otherwise stated)

| SYMBOL               | CHARACTERISTIC                                 | MIN | TYP  | MAX  | UNITS | CONDITIONS                                   |

|----------------------|------------------------------------------------|-----|------|------|-------|----------------------------------------------|

| BV <sub>GSS</sub>    | Gate to Source Breakdown Voltage               | -25 |      |      | V     | I <sub>G</sub> = -1µA, V <sub>DS</sub> = 0V  |

| V <sub>GS(off)</sub> | Gate to Source Cutoff Voltage                  | -1  | -3.5 | -6   | V     | V <sub>DS</sub> = 10V, I <sub>D</sub> = 1nA  |

| IDSS                 | Gate to Source Saturation Current <sup>2</sup> | 6   | 15   | 30   | mA    | V <sub>DS</sub> = 10V, V <sub>GS</sub> = 0V  |

| Igss                 | Gate Leakage Current                           |     | -1   | -500 | n۸    | V <sub>GS</sub> = -15V, V <sub>DS</sub> = 0V |

| lg                   | Gate Operating Current                         |     | -1   | -500 | pА    | V <sub>DG</sub> = 10V, I <sub>D</sub> = 5mA  |

| SYMBOL      | CHARACTERISTIC                 | MIN | TYP | MAX | UNITS  | CONDITIONS                                                   |  |

|-------------|--------------------------------|-----|-----|-----|--------|--------------------------------------------------------------|--|

| <b>g</b> fs | Forward Transconductance       | 4.5 | 6   | 9   | mS     | V <sub>DS</sub> = 10V, I <sub>D</sub> = 5mA, <i>f</i> = 1kHz |  |

| gos         | Output Conductance             |     | 70  | 200 | μS     | $v_{DS} = 10v$ , $I_D = 5IIIA$ , $I = 1KHZ$                  |  |

| Ciss        | Input Capacitance              |     | 3   |     | ъĘ     | $V_{22} = 10V_{12} = 5mA_{12} = 1MHz$                        |  |

| Crss        | Reverse Transfer Capacitance   |     | 1   |     | pF     | $V_{DS} = 10V, I_D = 5mA, f = 1MHz$                          |  |

| en          | Equivalent Input Noise Voltage |     | 4   |     | nV/√Hz | $V_{DS}$ = 10V, $I_{D}$ = 5mA, $f$ = 10kHz                   |  |

#### NOTES:

- 1. Absolute maximum ratings are limiting values above which serviceability may be impaired.

- 2. Pulse Test: PW  $\leq$  300µs Duty Cycle  $\leq$  3%

- 3. Assumes smaller value in numerator.

#### Over 30 Years of Quality Through Innovation

| FEATURE              | S                                     |                         |                        |  |  |  |  |  |

|----------------------|---------------------------------------|-------------------------|------------------------|--|--|--|--|--|

| ULTRA LC             | W DRIFT                               | ΔV <sub>GS1-2</sub> /Δ  | T│= 5µV/ºC max.        |  |  |  |  |  |

| ULTRA LC             | W NOISE                               | I <sub>G</sub> =80fA TY | Έ.                     |  |  |  |  |  |

| LOW NOIS             | SE                                    | e <sub>n</sub> =70nV/√  | Hz TYP.                |  |  |  |  |  |

| LOW CAP              | ACITANCE                              | C <sub>ISS</sub> =3pf m | ax.                    |  |  |  |  |  |

| ABSOLUT              | ABSOLUTE MAXIMUM RATINGS NOTE 1       |                         |                        |  |  |  |  |  |

| @ 25°C (u            | @ 25°C (unless otherwise noted)       |                         |                        |  |  |  |  |  |

| Maximum Temperatures |                                       |                         |                        |  |  |  |  |  |

| Storage T            | emperature                            |                         | -55 to +150°C          |  |  |  |  |  |

| Operating            | Junction Temperature                  |                         | -55 to +150°C          |  |  |  |  |  |

| Maximum              | Voltage and Current                   | for Each Tr             | ansistor <u>NOTE 1</u> |  |  |  |  |  |

| -V <sub>GSS</sub>    | Gate Voltage to Drain                 | or Source               | 40V                    |  |  |  |  |  |

| -V <sub>DSO</sub>    | Drain to Source Volta                 | ge                      | 40V                    |  |  |  |  |  |

| -I <sub>G(f)</sub>   | Gate Forward Curren                   | t                       | 10mA                   |  |  |  |  |  |

| -l <sub>G</sub>      | Gate Reverse Curren                   | 10µA                    |                        |  |  |  |  |  |

| Maximum              | Maximum Power Dissipation @ TA = 25°C |                         |                        |  |  |  |  |  |

| Continuou            | is Power Dissipation (T               | otal)                   | 500mW                  |  |  |  |  |  |

## LS830 LS831 LS832 LS833

#### ULTRA LOW LEAKAGE LOW DRIFT MONOLITHIC DUAL N-CHANNEL JFET AMPLIFIER

| SYMBOL                              | CHARACTERISTIC                  | MIN. | TYP. | MAX. | UNITS | CONDITIONS            |                       |          |